一 : 可编程逻辑器件

北 方 交 通 大 学 学 报第28卷第2期Vol.28No.2 文章编号:1000-1506(2004)02-0073-03

可编程逻辑器件在通用逆变器控制电路中的应用

童亦斌,刘京斗,叶晶晶

(北京交通大学电气工程学院,北京100044)

摘 要:随着对通用逆变器要求的不断提高,作为控制电路核心的微处理器的资源有时已不能

很好地满足控制电路设计的需要.结合分析采用传统数字电路进行扩展所存在的缺点,论述了

可编程逻辑器件在通用逆变器控制电路中的应用,并通过设计实例说明可编程逻辑器件的使

用可以极大地改善传统通用逆变器控制电路的设计.

关键词:电气工程;通用逆变器;可编程逻辑器件

中图分类号:TM464 文献标识码:B

ApplicationoftheProgrammableLogicDevice

inGeneralInverter’sControlCircuit

TONGYi_bin,LIUJing_dou,YEJing_jing

(SchoolofElectricalEngineering,BeijingJiaotongUniversity,Beijing100044,China)

Abstract:Themicroprocessorsareoftenusedasthecoreofthegeneralinverter’scontrolcircuit,

butitsresourceisbecomingmoreandmorescarce,speciallyinsomehighperformancedesign.

AfterdiscussingthedisadvantageofdesigningwithtraditionaldigitallogicICs,theapplication

andadvantageofusingtheprogrammablelogicdeviceinthecontrolcircuitofgeneralinverterare

discussed.

Keywords:electricalengineering;generalinverter;programmablelogicdevice

应的保护.

(3)模拟量的输入和处理.经过电平变换、滤波

等处理后的模拟量,一般送入F240内部的A/D转

换器进行转换.由于大部分处理都可由软件完成,因

此在通用逆变器的控制电路中,模拟输入通道的硬

件结构往往较简单.

(4)数字量的输入输出.数字量包括用户的给

定、运行状态反馈、状态指示以及开关量控制等.数

字量的输入输出既可通过F240的I/O口,也可以

利用片外扩展的I/O接口实现.

(5)总线扩展和逻辑.用于片外I/O接口和片

外存储器的扩展,总线扩展逻辑则包括产生片选信

号、读写控制等功能.

M、(6)外设接口.包括串行接口、串行EEPRO1 通用逆变器控制电路1.1 基本结构和主要功能通用逆变器一般采用微处理器作为控制电路的核心,其中又以集成有硬件PWM脉冲发生器的微处理器使用最为广泛.以较具代表性的TMS320F240[1](简称F240)为例,其控制电路的典型结构(参见图1)和主要功能是:(1)PWM脉冲的产生及处理.产生开关器件(大多采用IGBT)的控制脉冲;按要求对脉冲的极性进行处理;引入保护信号,保证故障和异常状态下IGBT的可靠保护.(2)运行状态监视、保护及中断.对逆变器的运行进行监视,在出现异常和故障时对逆变器实施相

收稿日期:2003-07-01

作者简介:童亦斌(1969—),男,浙江永康人,讲师,硕士.email:tongyibin@VIP.sina.com

叶晶晶 可编程逻辑器件

北 方 交 通 大 学 学 报 第28卷

实时时钟、显示等,常用于实现人机或双机通讯、信息存储等功能.这些功能一般通过F240与外部的

接口芯片配合完成.

图1 通用逆变器控制系统典型结构框图

Fig.1Typicalstructureofgeneral inverter’scontrolsystem

1.2 存在的缺点

充分利用F240的硬件资源,设计出以一片F240为核心的“单”芯片控制系统,在一些较简单的系统中就可以应付逆变器控制的要求.但是,随着对通用逆变器功能和要求的提高,F240的资源变得越来越紧张,这主要表现在:

(1)F240的I/O口多与片内外设的引脚复用,如果片内外设被充分利用,那么可用于数字量输入/输出的I/O口数量就会比较紧张.

(2)F240片内RAM较少,无法满足大规模采集、处理和保存数据的需要;另外,片内程序存储器有时还存在容量偏小和使用不便的问题.为此常需扩展片外存储器并设计相应的总线扩展逻辑电路.

(3)可靠完善的保护一般采用硬件直接保护和申请中断由软件保护相结合的方式,为此必须在F240外围设计一定数量的硬件逻辑电路.

(4)随着通用逆变器功能不断增强,F240本身的负担也越来越重,甚至无法满足需要,比如在高频变频器中利用软件实现死区时间补偿功能

[2]

.

为了解决类似问题,在一些高性能逆变器的设计中常需对F240进行外围电路扩展.但如果由功能固定、单一的传统数字电路(比如74AHC573、和门电路等)来实现,则存在以下缺点:

①微处理器的外围电路,特别是总线部分的电路,逻辑原理和结构都非常复杂,不利于设备的小型化和系统可靠性的提高.

②设计实现一些较复杂的功能(比如死区时间

补偿)不但非常困难而且也不现实.

③传统逻辑电路的硬连接缺乏灵活性,设计要求上的变化所带来的硬件电路修改,极易造成成本和开发效率的损失.

2 可编程逻辑器件PLD[3]

2.1 结构及特点

可编程逻辑器件(ProgrammableLogicDevice,PLD)主要包括可编程阵列逻辑(PAL)、通用阵列逻辑(GAL)、

可擦除可编程逻辑阵列(EPLD)、复杂可编程逻辑器件(CPLD)和现场可编程门阵列(FP-GA)等.与传统数字电路相比,PLD具有密度高、速度快、功耗小、可靠性高、使用灵活、保密性好、价格低廉等一系列优点,可方便地实现复杂的组合和时序逻辑.特别是采用在系统可编程技术后,可以在

线修改逻辑设计,使得硬件设计变得像软件一样灵活.凭借这些优点,PLD已在信息处理、智能仪表、自动控制等领域得到了广泛的应用.2.2 在通用逆变器控制电路中的应用

XILINX公司的XC9500系列CPLD

[4]

作为

PLD器件的典型代表,具有抗干扰能力强、在系统可编程、成本低廉和使用方便等优点,是通用逆变器控制电路设计的理想选择.对图1所示的通用逆变器控制系统,若将F240所有的外围数字电路都由CPL

D来实现,可以简化成图2所示的形式.

图2 采用PLD后通用逆变器控制系统结构框图Fig.2 StructuresketchofPLD_basedgeneral

61阅读提醒您本文地址:

inverter’scontrolsystem

如果PLD采用XC9500系列的XC9572,则其资源可根据具体的要求分别配置给:①与F240的STRB、W/R 、R/珨W、PS、DS、IS、A12~A15和D0~D3信号连接,实现PLD与F240的总线接口;②产生片外存储器的片选信号并扩展数字量输入输出端

叶晶晶 可编程逻辑器件

第1期 童亦斌等:可编程逻辑器件在通用逆变器控制电路中的应用

口;③输入外部的不同保护信号、经处理后产生PWM脉冲封锁和中断申请信号;④硬件PWM脉冲产生、死区时间设置和补偿功能,通过引入PWM脉冲指令、相电流极性信号、时钟和死区时间选择信号,产生最终的IGBT控制信号.

通过比较不难发现,可编程逻辑器件的采用对通用逆变器控制电路设计的改善主要表现在:

(1)采用PLD后,控制系统基本就由“F240+PLD”构成.电路芯片数目的减少不但对提高可靠性、减小电路尺寸有利,而且对降低通用逆变器器件采购、生成、调试和维护成本都有所帮助.另外,F240的外部总线结构也十分简洁,加上PLD的引脚和功能都可以根据PCB板布线的实际情况灵活地进行配置,这对简化电路板的设计和提高系统的电磁兼容性能十分有利.

(2)所有外部逻辑功能被封装在PLD内部,保密性较好.由于F240本身没有任何保密功能,利用PLD对硬件电路、以至于整个控制系统的设计进行保密成为最简便的方法之一.

(3)绝大多数逻辑功能和引脚都可通过PLD的编程来实现,使电路原理、电路板及控制软件的开发可先于、并独立于具体的外部逻辑设计进行,达到避免浪费、降低成本和提高效率的目的,这在设计、调试、小批量试制和实验阶段非常吸引人.

(4)利用PLD可以方便地设计出复杂的功能(包括前面介绍的多级保护和死区时间补偿功能),提高系统的可靠性和软件运行的效率.以死区时间补偿为例,利用PLD实现的硬件补偿比用软件实现每个开关周期平均少花费约2μs的计算时间,这对高频变频器来说十分可观.

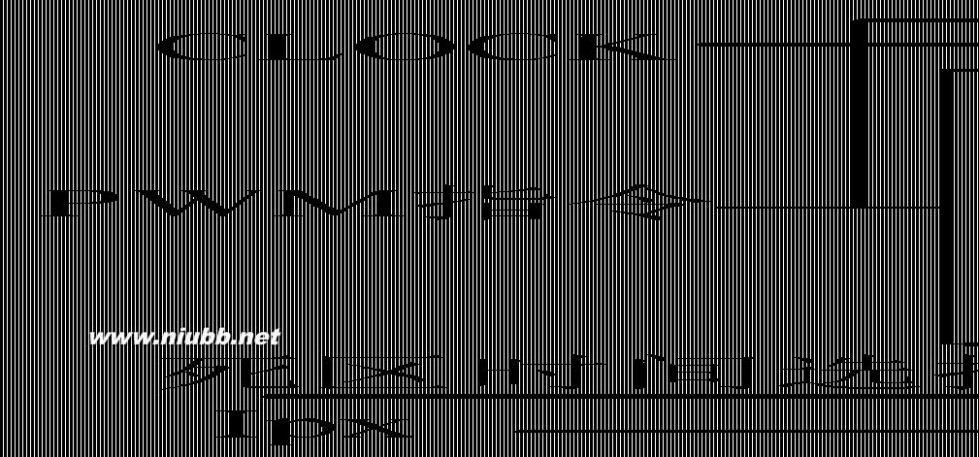

图

3为利用PLD实现死区时间发生和补偿的

图3 利用PLD实现死区时间发生和补偿的逻辑原理

Fig.3 LogicalprincipleofPLD_Baseddead

timegenerationandcompensation

逻辑原理

[5]

,其中CLOCK、Ipx、Vgx1和Vgx2分别

为工作时钟、相电流极性信号、上桥臂和下桥臂IG-BT的控制脉冲.

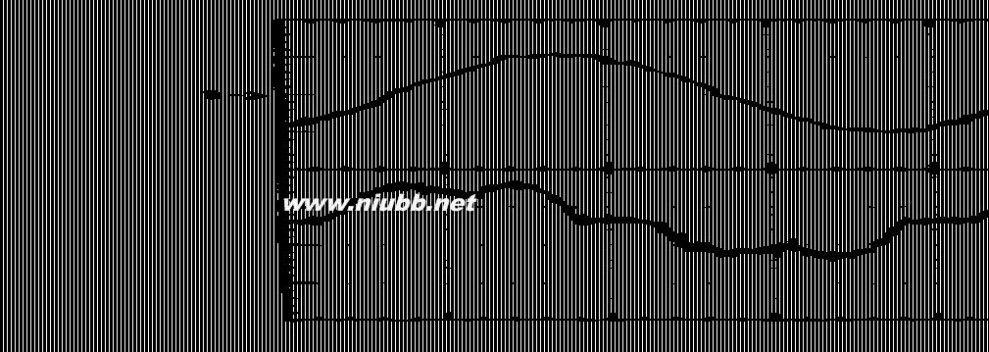

图4是利用PLD实现死区时间补偿的实验结果(开关频率3kHz,死区时间20μs).实验结

果表明效果十分理想.

(a)输出频率5Hz

(b)输出频率25Hz(50ms/div)

(10ms/div)

图4 利用PLD实现死区时间补偿实验结果Fig.4 ExperimentalresultsofPLD_Baseddeadtimecompensation(Lower:

beforecompensation,Upper:aftercompensation)

3 结论

可编程逻辑器件的采用不但可以更好地兼顾通用逆变器对可靠性、小型化、低成本、高性能等多方面日益提高的要求,而且可使控制电路的设计变得灵活和高效,对提高开发、生产和维护效率也有很大的帮助.参考文献:

[1]TexasInstrumentsCorporation.TMS320F/C240DSP

ControllersReferenceGuide[Z].1999.

[2]余功军,钟彦儒,杨耕.一种IGBT变频器死区时间的补

偿策略[J].电力电子技术,

1997,(4):7-9.YUGongjun,ZHONGYanru,Yanggeng.AstrategyofDead_TimeCompensationforIGBTInverter[J].Powerelectronics,1997,(4):

7-9.(inChinese)[3]曾繁泰,候亚宁.可编程器件应用导论[M].北京:清华

大学出版社,2001.

ZENGFan_tai,HOUYa_nin.ApplicationInstructionofProgrammableDevice[M].Beijing:TsinghuaUniversityPublishingHouse,2001.(inChinese)

[4]XILINXCorporation.XC9500In_SystemProgrammable

CPLDFamily[Z].1999.

[5]BertoS.FPGA_BasedRandomPWMwithReal_Time

DeadTimeCompensation[J].IEEE,PESC032003,(2):15-19.

61阅读提醒您本文地址:

二 : ALTERA可编程逻辑器件全系列产品75

Altera公司(NASDAQ: ALTR)是可编程逻辑解决方案的倡导者,帮助系统和半导体公司快速

高效地实现创新,突出产品优势,赢得市场竞争。Altera的FPGA、SoC FPGA、CPLD和HardCopy? ASIC结合软件工具、知识产权、嵌入式处理器和客户支持,为全世界13,000多名客户提供非常有价值的可编程解决方案。Altera成立于1983年,2010年年度收益达到19.5亿美元。Altera总部位于加州圣何塞,拥有分布在19个国家的2,600多名员工。

深圳市恒大创新科技有限公司是ALTERA半导体公司大陆地区的专业增值分销商,公司主营

高端可编程逻辑器件系列芯片,主要包括PLD系列和FPGA系列的产品,我们能够给您提供最优的价格,最好的服务,及时稳定的供货,以及强大的技术支持。

一.Altera支持28-Gbps的FPGA适于下一代100G以上系统

Altera日前宣布开始发售世界上第一款具有28-Gbps收发器的FPGA。Stratix? V GT器件

是业界目前为止带宽最大、性能最好的FPGA。这一业界领先的创新Stratix V GT FPGA技术为

前沿通信系统设计人员量身定做,帮助他们尽快实现市场解决方案,以满足越来越高的网络带宽要求。StratixV GT FPGA支持互联网与互联网协议(IP)服务和应用中迅速增长的网络数据量需

求。JDSU等创新公司采用了Altera解决方案,在其下一代测试和测量解决方案中最先使用这一最先进的技术。JDSU通信测试和测量业务部副总裁兼总经理LarsFriedrich评论说:“JDSU的客户要求我们的解决方案采用前沿技术,而与Altera合作保证了我们能够顺利交付最先进的仪表,帮助用户实施高性能宽带通信应用。作为唯一带有28-Gbps收发器的FPGA,StratixV GT FPGA使我们能够在系统中实现最复杂的功能,支持最佳性能和数据吞吐量。”

StratixV GT FPGA综合了Altera超过十年内采用业界性能最好的28-nm工艺技术(28HP),

部开发的收发器创新技术。器件通过四个28-Gbps收发器、32个全双工12.5-Gbps收发器以及

2133 Mbps的4x72位DIMMDDR3存储器接口,支持背板、光模块和芯片至芯片应用。

Stratix V GT FPGA中的28-Gbps收发器满足CEI-28G规范要求,每通道功耗只有200 mW,大幅度降低系统单位带宽功耗。您可以在Altera网站上观看展示Stratix V GT FPGA收发器性能的

视频,名为“先睹为快:业界第一款28-Gbps FPGA”。StratixIV GT FPGA专门针对通信系统、高端测试设备和军用通信系统等最新一代40G/100G应用进行优化。器件集成度非常高,包括622K逻辑单元(LE)、512个18x18乘法器、硬核PCI Express? (PCIe?)、10 Gbps以太网(10GbE)以

及Interlaken知识产权模块,支持最新的高速串行协议。Altera产品市场资深总监

Patrick Dorsey评论说:“定制28-nm技术含有性能最好的工艺和最先进的收发器技术,利用这一技术,我们帮助JDSU等用户突破了带宽限制,令他们能够充满信心的迅速将最前沿系统推向市场。业界目前发售的其他FPGA还不能实现Stratix V GT FPGA所提供的带宽和功效,只有这一FPGA能够让我们客户的产品更灵活、可靠性更高,应用范围更广。”

二. Altera推出Cyclone IV GX/E FPGA系列

Altera拓展其成功的Cyclone FPGA系列并延续其收发器技术领先优势,于近日发布了

Cyclone IV FPGA新系列。在移动视频、语音和数据访问以及高质量3D图像对低成本带宽需求

的推动下,Cyclone IV FPGA系列增加了对主流串行协议的支持,不但实现了低成本和低功耗,而且还提供丰富的逻辑、存储器和DSP功能。

Cyclone IV FPGA系列有两种型号。Cyclone IV GX器件具有150K逻辑单元(LE)、6.5-Mbit

RAM、360个乘法器,以及8个支持主流协议的集成3.125-Gbps收发器,这些协议包括千兆以太网(GbE)、SDI、CPRI、V-by-One,Cyclone IV GX还为PCI Express (PCIe)提供硬核IP。这些

低功耗器件封装大小只有11x11 mm,非常适合无线、固网、广播、工业和消费类等市场的低成

本、小型封装应用。Cyclone IV E器件前所未有的同时实现了低成本、高性能和低功耗,在手

持式软件无线电等低功耗应用中,其功耗比以前的Cyclone产品低25%。

对于Cyclone IV GX器件,Altera重点放在降低系统总成本上。与前几代结合外部收发器

PHY的Cyclone产品相比,Cyclone IV GX FPGA通过集成收发器降低了外部元件成本,功耗减小了30%。低功耗意味着不需要采用热沉硬件,因此,也降低了成本。Cyclone IV GX器件只需要两路电源供电,大大简化了PCB设计,减小了电路板面积,降低了成本。Cyclone IV GX最小的器件开发重点放在低成本上,是业界最小的收发器FPGA。

三.Altera Stratix IV E FPGA开发套件具530K逻辑单元FPGA

Altera 公司日前宣布推出其面向 Stratix IV FPGA 的最新开发套件。Stratix IV E FPGA 开

发套件具有业界最高密度、最高性能的 FPGA。该套件为用户提供了全面的设计环境,其中包括迅速开始其高密度原型产品设计所需的硬件和软件。

Stratix IV E FPGA 开发套件基于高性能、高密度的 Stratix IV EP4SE530 FPGA。该 FPGA

具有 530K 逻辑单元 (LE),比当前市场上同类竞争产品的 FPGA 性能平均高 25%。Stratix IV EP4SE530 FPGA 所具有的性能和密度优势,让使用 Stratix IV E FPGA 开发套件的广大用户能够在单器件中容纳其诸多大型设计,并实现快速时序收敛。

Stratix IV E FPGA 开发套件是第一款具有 533-MHz DDR3 DIMM 接口的 FPGA 套件。利用

该套件,用户可以开发并测试许多由 DDR3 DIMM、QDR II+ 和 RLDRAM II 存储器接口组成的存储器子系统。

Stratix IV EP4SE530 FPGA 与 Stratix III FPGA 和 Stratix IV EP4SE820 FPGA 引脚兼

容。这种引脚兼性使得用户可以无缝地将其 Stratix III FPGA 设计移植到一个更更高密度的 Stratix IV E FPGA。现在用户可以无缝地将其最终的 Stratix IV E FPGA 转换为 Altera 低成本 HardCopy IV E ASIC。根据 2010 年新推出的硅芯片用户还可以将其设计移植到更高密度的EP4SE820 器件,EP4SE820 器件是由 Altera 于 2009 年9 月份推出的。

Stratix IV E FPGA 开发套件包括:

·具有 Stratix IV E EP4SE530 FPGA 的开发板

·具有设计示例的板卡测试系统

·具有 72-bit 数据总线的 2-GB DDR3 SDRAM DIMM

·具有 18-bit 数据总线的 72-Mb QDR II+ SRAM 器件

·具有 36-bit 数据总线的 576-Mb RLDRAM II CIO 器件

·包含设计示例的 CD-ROM

·Nios II 设计套件许可

·开发套件版 (DKE) Quartus II 设计软件

四.Altera发布远程射频前端设计CPRI v4.1 IP内核

Altera公司日前宣布,开始提供通用公共射频接口(CPRI) v4.1知识产权(IP)内核。CPRI

v4.1 IP内核可实现高达6.144 Gbps的通道速率,在一个系统中支持LTE和WiMAX标准,并为

WCDMA、CDMA和其他空中接口标准提供传统的支持。它帮助开发人员将专用CPRI轻松更新到能够灵活配置的解决方案,支持目前的标准,提高用户的效能,降低总成本。

这一可全面配置的现成解决方案完善了Altera的40-nm系列产品,该系列产品包括支持

3.072G CPRI线路速率的Arria II GX FPGA,以及支持6.144G CPRI线路速率的Stratix IV GX FPGA和HardCopy IV ASIC解决方案。这一IP内核面向多种无线应用,包括多模空中接口支持,单跳和多跳系统拓扑以及高级MIMO天线配置等。它还提供测试台,完成常见配置模式的启动排序,因此,开发人员能够迅速开始设计,把精力集中在突出产品优势上。

Altera CPRI v4.1 IP内核包括以下关键特性:

·对CPRI v4.1的内置支持,后向兼容映射方法。

·支持6.144 Gbps线路速率只需要低至153.6 MHz的时钟速率,简化了时序逼近。

·每个IP内核24路天线载波

·集成10/100以太网MAC和HDLC控制器

这一新的CPRI v4.1内核进一步提高了Altera系列无线基站技术,它包括IP、参考设计和

DSP Builder工具,支持开发数字下变频(DDC)、数字上变频(DUC)、峰值因子抑制(CFR)、数字

预失真(DPD)等其他功能。

五.Altera扩展低成本CPLD MAX II,应用至便携式产品

Altera公司日前扩展了MAX II器件系列,以满足不断发展的便携式应用市场的需求。MAX

II器件采用了新的超小外形封装和新型关断功能,据称是业界成本最低的器件,手持式应用设

计人员使用该器件后,成本和功耗仅是竞争产品的一半。Altera MAX II CPLD满足了点对多点

(PMP)系统、条形码扫描器、PDA和手持式传感器等便携式系统设计人员对小外形封装和低功耗

功能的要求。

Intercoastal电子公司系统工程师Mark Chaildin说:“评估了多种元件方案后,我们认

为MAX II最适合我们的多路集成激光工作系统(MILES)的电池供电无线激光传感器。MAX II器件的低功耗、迅速上电以及密度和低成本优势帮助我们在市场上赢得了竞争。”

据Gartner Dataquest报告,消费类市场便携式应用CAGR为9%,预计将从2006年的160

亿美元增长到2008年的190亿美元。新的MAX II超小外形封装和关断功能针对这一市场而开发,将促进MAX II器件在便携式领域的应用。

Altera称,MAX II EPM240、EPM570和EPM1270器件现在提供100引脚和256引脚0.5mm Micro

FineLine BGA (MBGA)封装和100引脚1.0mm FineLine BGA (FBGA)封装。与竞争CPLD方案相比,

设计人员使用新的MBGA封装后,在相同的电路板面积上,用户I/O和逻辑单元(LE)数量平均多出50%。这使得MAX II CPLD非常适合单位电路板面积上(mm2)需要较多I/O与LCD显示器、小

键盘、闪存和存储器进行接口的应用。设计人员利用新封装和MAX II器件独有的特性(较高的逻辑密度、片内电压稳压器和内部振荡器),能够进一步降低系统成本,集成分立器件,减少电源数量。

据称,MAX II CPLD具有最低的动态功耗——比竞争CPLD方案的功耗低50%以上,还具有能

够延长电池使用时间的关断功能。与竞争CPLD不同,MAX II器件的功耗特性能够关断器件,完全切断电流吸收。

六.Altera推出性能更高成本更低的HardCopy Stratix器件

Altera公司发布了HardCopy Stratix器件系列最新一代低成本掩模可编程器件。现在,设

计者采用Altera的3.0版QuartusII这个FPGA前端,即可在设计开始阶段使用其独特的设计流程着手大批量的HardCopy器件。HardCopy Stratix器件据称是业界唯一从原型到批量成品进行大容量设计的完整解决方案,借助了Altera的Stratix FPGA灵活性、功能和及时面市的诸多优势。HardCopy Stratix器件使FPGA的性能改良最高达100%,并能够享有ASIC的优点,将ASIC高昂的开发成本降到最低,漫长的设计周期缩到最短。相比最初推出的HardCopy APEX系列,全

新HardCopy Stratix实现同等的逻辑功能,具有更高的性能,更低的功耗,成本更降低

30%。

采用HardCopyStratix设计的系统厂商可选择保持原有的性能,或者将性能提高50%,在某

些情况下可提高100%。功耗也降低了40%。Altera关注降低成本来帮助客户满足他们系统的成

本要求。进一步提高逻辑单元的结构和HardCopy Stratix体系的布线效率,同样的功能下

HardCopyStratix节省的成本是最初HardCopy APEX器件的30%。HardCopy Stratix器件保持了StratixFPGA同样的先进特性,包括层次化时钟结构、TriMatrix存储器和优化的嵌入数字信号处理(DSP)模块。和Stratix器件系列一

样,HardCopy Stratix器件之处同样广泛

的高速接口――包括SPI-4.2、10千兆以

太网(XSBI)和RapidIO标准,以及各种高

速I/O标准包括LVDS、LVPECL和

HyperTransport标准。这使无风险、无缝

迁移成为可能。

HardCopy Stratix设计流程使设计

者可以在设计初期针对HardCopy器件进

行设计,同时充分利用

Altera HardCopy Stratix器件的性能和

改善功耗改良的优势。从一开始,设计者就能够用3.0版Quartus II设计软件,根据

HardCopy Stratix器件上的实际逻辑布局来验证时限、性能和估计功耗。所有这些功能都包括

在2,000美元一套的设计工具中,现在已有数以万计的工程师正在使用这套工具。ASIC设计者

关心如何降低整体成本,让他们的产品在更短的时间内面市,现在新的Quartus II软件能够助其赢得这个设计目标。所有的AlteraHardCopy器件都采用通用的基本阵列,具有和相应FPGA

相同的体系,只有首两层金属层专门用来实现客户设计。HardCopy器件结构的增强包括更短的

路径走线,缩小内核尺寸和 去除同FPGA可编程性相关的硅结构,这样内核尺寸比最初的

Stratix FPGA器件减小了60%到70%。HardCopy Stratix器件是用和Stratix FPGA同样可靠的、先进的0.13微米CMOS工艺生产的。HardCopy Stratix器件系列包括五个产品,容量从25,660到79,040个逻辑单元(LE)。所有的器件都有BGA封装。

深圳市恒大创新科技有限公司创建于公元2006年,除了从事电子元器件贸易外,在半导体产品领域最初为一家小型半导体技术支持提供商,从高压非标电源技术开始,我们逐步发展融入到锂电池技术、RFID、AVR、工控技术、光纤通讯、医疗设备、仪器仪表、电力设备、航空航天等领域半导体方案推广。我公司目前已经成功代理SINOWEALTH(中颖)单片机、COILCRAFT(线艺)电感和OMNIVISION(豪威)图象传感器,并成为国际知名品牌NXP、ADI、TI、ST、ON、 IR、NS、AVAGO、MAXIM、ATMEL、MINI-CIRCUITS、MICREL、MICROCHIP、INFINEON、INTERSIL、DAVICOM、MARVELL、SENSIRION的专业增值分销商,另外在ATMEL、ST、XILINX和ALTERA宇航产品等偏冷门军品集成电路芯片方面有较强的资源优势。

按照立足海外采购,面向国内服务的需求,除了香港的采购中心、香港新界的物流储仓和深圳市恒大创新科技有限公司(运行中心)外,都还在德国慕尼黑、北美、以色列、日本、香港、台湾建有採购合作中心、技术支持中心、产品支持中心和客户服务中心,并且在中国一直和台湾友尚企业、世健系统、 伟博电讯、世平基通储仓、昭田电气、MOUSER、爱益华、品佳、安富利、新晔、文晔、联宝中国等国际知名元件代理保持亲密合作关系。感谢广大客户的支持和信赖以及公司全体员工的共同努力,我们用多年时间把公司发展成为科技产品研发,电子产品贸易和电子产品製造为一体的恆大创新实业股份有限公司。

恆大创新实业股份有限公司同时也是亚太地区优秀的电子产品研发制造及电子产品周边零件供应商和增值服务商之一,经过近6年的发展,已成为中国优秀的电子产品技术和销售服务商。通过遍布全国的零售网络、连锁销售中心和新近开通的电子商务网站,服务于包括军用及商用客户。

国有企业:中国科学研究院兰州研究所、中国航空工业总公司洛阳613所、中国航空工业第608研究所、铁道部株洲电力机车研究所、中国船舶重工集团7院722所、中国运载火箭技术研究所、国营711所、中国信息产业部40所、等中国军备企业。

合作院校:长沙国防科技大学、武汉华中科技大学、上海复旦大学、大连理工大学、长春光华学院等中国高科技技术英才之教育机构。

恒大创新实业股份有限公司

深圳市恒大创新科技有限公司

服务据点:香港 深圳 北京 上海 成都 长沙 东莞 宁波

----------------------------------------------------

联系人:侯顺涛 销售主管 Mobile:13631588303

主营业务:国际半导体通路 产品方案及开发 OEM/ODM制造

ADD:香港.新界.沙田火炭坳背湾街45-47喜利佳工业大厦10-O 座

TEL:00852-63385528 FAX:00852-26014125

ADD:深圳市福田区益田路3008号皇都广场A座1304-1305室(会展中心南侧)

TEL:86-755-88250080-8009 FAX:86-755-88250089

Emial:houst@cnhenda.com WEB:www.cnhenda.com

MSN:houshuntao@hotmail.com QQ:228289156

-----------------------------------------------------

上善若水,水善利万物而不争。

三 : 可编程逻辑器件及EDA技术考试题

可编程逻辑器件及EDA技术试卷

专业班级: 姓名: 学号:

一.选择题(20分)

1. 大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是____。(www.61k.com]

A. FPGA全称为复杂可编程逻辑器件;

B. FPGA是基于乘积项结构的可编程逻辑器件;

C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;

D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

2. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述________。

A. 器件外部特性 B. 器件的内部功能

C. 器件外部特性与内部功能 D. 器件的综合约束

3.进程中的信号赋值语句,其信号更新是_______。

A.按顺序完成; B.比变量更快完成;

C.在进程的最后完成; D.都不对。

4. 不完整的IF语句,其综合结果可实现____。

A. 时序逻辑电路 B. 组合逻辑电路

C. 双向电路 D. 三态控制电路

5.在VHDL语言中,下列对时钟边沿检测描述中,错误的是_____。

A. if clk’event and clk = ‘1’ then

B. if falling_edge(clk) then

C. if clk’event and clk = ‘0’ then

D.if clk’stable and not clk = ‘1’ then

6.下列语句中,不属于并行语句的是:_______

A.进程语句

B.CASE语句

C.元件例化语句

D.WHEN?ELSE?语句

7.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是:_______

A.PROCESS为一无限循环语句

B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动

C.当前进程中声明的变量不可用于其他进程

D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成

8.VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库:_______

可编程逻辑器件 可编程逻辑器件及EDA技术考试题

A.IEEE库 B.VITAL库 C.STD库

D.WORK工作库

9. 电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);下列方法中______不属于面积优化。(www.61k.com] A. 流水线设计 B. 资源共享 C. 逻辑优化 D. 串行化 10.下列EDA软件中,哪一个不具有逻辑综合功能:________。 A. Max+Plus II B. ModelSim C. Quartus II D. Synplify

二.EDA名词解释(15分)

写出下列缩写英文含义:

1. ASIC 2. FPGA 3. CPLD 4. EDA 5. IP

三.简答题 (25分)

1:说明信号与变量的功能特点,以及应用中的异同点 2:简述EDA的设计流程

3:TYPE 与 SUBTYPE 的区别

4:Moore 型和 Mealy 型两类状态机的区别 5:FPGA 与 CPLD 的结构区别

四.写VHDL程序(20分)

1. 数据选择器MUX,其系统模块图和功能表如下图所示,试用VHDL描述该数据选择器MUX。

SEL00

COUTA or BA xor BA and BA nor B“XX”

011011OTHERS

2.阅读下列原理图,写出VHDL程序(RTL级)

可编程逻辑器件 可编程逻辑器件及EDA技术考试题

五.设计(20分)

试用VHDL设计一个带计数使能的异步复位计数器。(www.61k.com)

输入端口: clk 时钟信号

rst 异步复位信号

en 计数使能

load 同步装载

data (装载)数据输入,位宽为10

输出端口: q 计数输出,位宽为10

本文标题:可编程逻辑器件-可编程逻辑器件61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1