一 : 移位寄存器设计verilog

电 子 科 技 大 学

ASIC课程设计报告一

学 号 : 201222240937 姓 名 : 周 恒 课题题目 : 移位寄存器设计

2013年5月

verilog移位寄存器 移位寄存器设计verilog

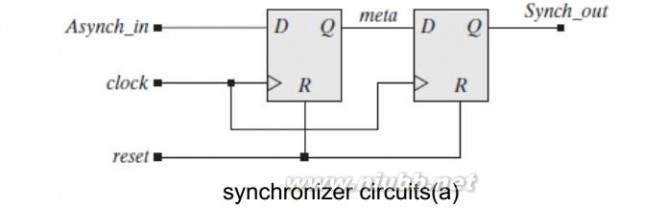

1. Write and verify the Verilog models for the two basic types of synchronizer circuits(a,b) shown in Fig.1

本电路实现是功能是一个两位的移位寄存器。[www.61k.com]Asynch_in为输入,

Synch_out为输出,clock是时钟,reset为异步复位信号。

电路a的verilog代码为:

module syn_a(

input Asynch_in,

input clock,

input reset,

output Synch_out);

wire meta;

reg Q1,Q2;

assign meta=Q1;

assign Synch_out=Q2;

always @(posedge clock or negedge reset)

begin

if(!reset)begin

Q1 <=1'b0;

Q2 <=1'b0;

end

else begin

Q1 <= Asynch_in;

Q2 <= meta;

end

end

endmodule

验证代码:

`timescale 1ns/1ps

module syn_a_test;

reg Asynch_in;

reg clock;

reg reset;

wire Synch_out;

always #50 clock=~clock;

verilog移位寄存器 移位寄存器设计verilog

initial

begin

clock=1;

reset=1;

Asynch_in=1;

#50 reset=0; Asynch_in=0;

#50 reset=1;

#50 Asynch_in=1;

#100 Asynch_in=0;

#200 Asynch_in=1;

#100 Asynch_in=0;

#100 Asynch_in=1;

#100 Asynch_in=0;

#100 $stop;

end

syn_a

a(.Asynch_in(Asynch_in),.clock(clock),.reset(reset),.Synch_out(Synch_out));

endmodule

输出波形:

从输出波形可以看出输出比输入延迟一个时钟,电路功能正确。(www.61k.com]

电路

b

电路b的verilog代码:

module syn_b(

input Asynch_in,

input clock,

verilog移位寄存器 移位寄存器设计verilog

input reset,

output reg Synch_out);

wire Clr,Clr_in;

reg q1,q2;

always @(posedge Asynch_in or negedge Clr) if(!Clr)

q1<=1'b0;

else

q1<=1'b1;

always @(posedge clock or negedge Clr) if(!Clr)

q2<=1'b0;

else

q2<=q1;

always @(posedge clock or negedge reset) if(!reset)

Synch_out<=1'b0;

else

Synch_out<=q2;

and (Clr_in,!Asynch_in,Synch_out); or (Clr,Clr_in,reset);

endmodule

验证代码:

`timescale 1ns/1ps

module syn_b_test;

reg Asynch_in;

reg clock,reset;

wire Synch_out;

always #50 clock=~clock;

initial

begin

clock=1;

reset=1;

Asynch_in=1;

#30 reset=0;

#20 Asynch_in=0;

#50 reset=1;

#50 Asynch_in=1;

verilog移位寄存器 移位寄存器设计verilog

#100 Asynch_in=0;

#200 Asynch_in=1;

#100 Asynch_in=0;

#100 Asynch_in=1;

#100 Asynch_in=0;

#100 Asynch_in=1;

#100 reset=0;

#50 reset=1;

#100 Asynch_in=0;

#200 Asynch_in=1;

#100 Asynch_in=0;

#100 Asynch_in=1;

#100 Asynch_in=0;

#100 Asynch_in=1;

#100 $stop;

end

syn_b

b(.Asynch_in(Asynch_in),.clock(clock),.reset(reset),.Synch_out(Synch_out));

endmodule

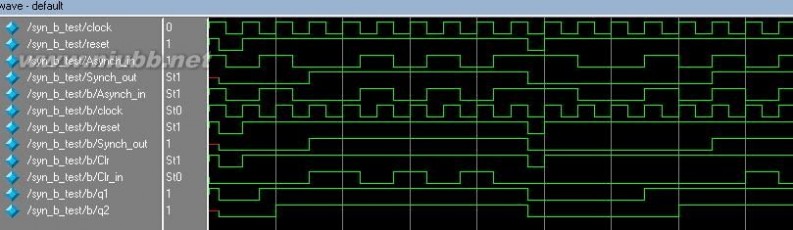

modelsim仿真波形:

二 : .艾米电子 - 移位寄存器,Verilog

对读者的假设

已经掌握:

内容

free-running移位寄存器

自由运行移位寄存器,即在每一个时钟周期内,寄存器的内容会被左移或右移一位。[www.61k.com]该寄存器没有其他的控制信号。

代码1 free-running移位寄存器

module free_run_shift_reg #(parameter N=8) ( // global clock and asyn reset input clk, input rst_n, // serial I/O interface input s_in, output s_out ); // signal declaration reg [N-1:0] r_reg; wire [N-1:0] r_next; // body // register always@(posedge clk, negedge rst_n) if(!rst_n) r_reg <= 0; else r_reg <= r_next; // next-state logic assign r_next = {s_in, r_reg[N-1:1]}; // output logic assign s_out = r_reg[0]; endmodule次态(next-state)逻辑是一位移位器,作用是将r_reg右移一个位置,然后在最高位(MSB)插入串型输入s_in。由于1位移位器仅需要重新连接输入和输出信号,因此不需要任何实际的逻辑电路。

Universa shift register

通用移位寄存器可以载入并行数据,然后左移或者右移,抑或保持原有状态。它可实现并串操作(先载入并行输入,然后移位输出),或者串并转换(先移位输入,然后一并输出)。

代码2 万用移位寄存器

module univ_shift_reg #(parameter N=8) ( // global clk and asyn reset input clk, input rst_n, // serial I/O interface input [1:0] ctrl, input [N-1:0] d, output [N-1:0] q ); // signal declaration reg [N-1:0] r_reg, r_next; // body // register always@(posedge clk, negedge rst_n) if(!rst_n) r_reg <= 0; else r_reg <= r_next; // next-state logic always@* case(ctrl) 2'b00: r_next = r_reg; // no operation 2'b01: r_next = {r_reg[N-2:0], d[0]}; // shift left 2'b10: r_next = {d[N-1], r_reg[N-1:1]};// shift right defaut: r_next = d; endcase // output logic assign q = r_reg; endmodule次态逻辑使用了一个4选1的多路选择器来选择寄存器所需的次态值。注意:d的最低位和最高位(d[0]和d[N-1)被用作左移操作和右移操作的串型输入。

参考

1 Pong P. Chu.FPGA Prototyping By Verilog Examples: Xilinx Spartan-3 Version.Wiley

另见

[与艾米一起学FPGA/SOPC].[逻辑实验文档连载计划]

扩展:移位寄存器 verilog / 4位移位寄存器verilog / 8位移位寄存器verilog

三 : FPGA Verilog HDL 系列实例--------双向移位寄存器

【连载】 FPGA Verilog HDL 系列实例

Verilog HDL 之 双向移位寄存器

一、原理

前一个实验设计的寄存器只有寄存数据和代码的功能。[www.61k.com]有时为了处理数据,需要将寄存器中的各位数据在移位控制信号的作用下,依次向高位或是低位移动移位。具有移位功能的寄存器称为移位寄存器。

本实验就是设计一个双向的移位寄存器,该寄存器可以对4位信号串行输入的数据进行移动输出。另外,该寄存器还有一个异步清零端,低电平有效。还有一个load装载数据的信号输入,用于预置数据,还有一个控制左移或是右移的信号输入,其功能表如表1.1所示。

表1.1 双向移位寄存器功能表

二、实现

在设计文件中输入Verilog代码

1 `timescale 1 ns / 1 ps

2

3 module shiftdata ( left_right ,load ,clr ,clk ,DIN ,DOUT );

4

5 input left_right ;

6 wire left_right ;

7 input load ;

8 wire load ;

9 input clr ;

10 wire clr ;

11 input clk ;

12 wire clk ;

13 input [3:0] DIN ;

14 wire [3:0] DIN ;

15

16 output [3:0] DOUT ;

17 wire [3:0] DOUT ;

18 reg [3:0] data_r;

19

20 assign DOUT = data_r ;

21

22 always @ ( posedge clk or posedge clr or posedge load )

23 begin

24 if ( clr == 1)

25 data_r <= 0;

26 else if (load )

27 data_r <= DIN;

28 else begin

29 if ( left_right)

30 begin

31 data_r <= (data_r<<1);

32 data_r[0] <= 0;

33 end

34 else begin

35 data_r <= (data_r>>1);

36 data_r[3] <= 0;

37 end

38 end

39 end

40

41 endmodule

扩展:移位寄存器 verilog / 4位移位寄存器verilog / 8位移位寄存器verilog

本文标题:verilog移位寄存器-移位寄存器设计verilog61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1