一 : OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CNOpenCV参考手册

版本2.1

2010年3月18日

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

opencv中文论坛 OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CN

第一部分

C API参考

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

opencv中文论坛 OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CN

第一章

cxcore核心功能

1.1基本结构

CvPoint

二维点整数坐标(通常以0为基坐标)

typedef struct CvPoint

{

int x;

int y;

}

CvPoint;

x x坐标

y y坐标

/*构造函数*/

inline CvPoint cvPoint(int x,int y);

/*从CvPoint2D32f转换*/

inline CvPoint cvPointFrom32f(CvPoint2D32f point);CvPoint2D32f

二维点浮点坐标

typedef struct CvPoint2D32f

{

float x;

float y;

}

CvPoint2D32f;

x x坐标

y y坐标

/*构造函数*/

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

opencv中文论坛 OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CN

inline CvPoint2D32f cvPoint2D32f(double x,double y);

/*从CvPoint转换*/

inline CvPoint2D32f cvPointTo32f(CvPoint point);

CvPoint3D32f

三维点浮点坐标

typedef struct CvPoint3D32f

{

float x;

float y;

float z;

}

CvPoint3D32f;

x x坐标

y y坐标

z z坐标

/*构造函数*/

inline CvPoint3D32f cvPoint3D32f(double x,double y,double z);CvPoint2D64f

二维点双精度浮点坐标

typedef struct CvPoint2D64f

{

double x;

double y;

}

CvPoint2D64f;

x x坐标

y y坐标

/*构造函数*/

inline CvPoint2D64f cvPoint2D64f(double x,double y);

/*从CvPoint转换*/

inline CvPoint2D64f cvPointTo64f(CvPoint point);

CvPoint3D64f

三维点双精度浮点坐标

typedef struct CvPoint3D64f

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

opencv中文论坛 OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CN

{

double x;

double y;

double z;

}

CvPoint3D64f;

x x坐标

y y坐标

z z坐标

/*构造函数*/

inline CvPoint3D64f cvPoint3D64f(double x,double y,double z);CvSize

像素级的矩形的大小

typedef struct CvSize

{

int width;

int height;

}

CvSize;

width 矩形的宽度

height 矩形的高度

/*构造函数*/

inline CvSize cvSize(int width,int height);

CvSize2D32f

亚像素级的矩形的大小

typedef struct CvSize2D32f

{

float width;

float height;

}

CvSize2D32f;

width 矩形的宽度

height 矩形的高度

/*构造函数*/

inline CvSize2D32f cvSize2D32f(double width,double height);

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

opencv中文论坛 OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CN

CvRect

矩形的大小和位置(通常是左上角)

typedef struct CvRect

{

int x;

int y;

int width;

int height;

}

CvRect;

x 左上角的x坐标

y 左上角的y坐标(对于Windows bitmaps为左下角)

width 矩形的宽度

height 矩形的高度

/*构造函数*/

inline CvRect cvRect(int x,int y,int width,int height);

CvScalar

承载一、二、三、四维双精度浮点数的容器

typedef struct CvScalar

{

double val[4];

}

CvScalar;

/*构造函数:

根据val0初始化val[0],val1初始化val[1]等等

*/

inline CvScalar cvScalar(double val0,double val1=0,double val2=0,double val3=0);/*构造函数:

将val[0]至val[3]初始化为val0123

*/

inline CvScalar cvScalarAll(double val0123);

/*构造函数:

将val[0]初始化为val0,val[1]至val[3]初始化为0

*/

inline CvScalar cvRealScalar(double val10);

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

opencv中文论坛 OpenCV参考手册

HTTP://WWW.OPENCV.ORG.CN

CvTermCriteria

迭代算法终止条件

#define CV_TERMCRIT_ITER

#defineCV_TERMCRIT_NUMBER

#defineCV_TERMCRIT_EPS

typedef struct CvTermCriteria

{

int type;

int max_iter;

double epsilon;

}

CvTermCriteria;

type CV_TERMCRIT_ITER与CV_TERMCRIT_EPS的联合

max_iter 迭代最大次数

epsilon 所需精度

/*构造函数*/

inline CvTermCriteria cvTermCriteria(int type,int max_iter,double epsilon);

/*检查并转换一个CvTermCriteria以至于使type=CV_TERMCRIT_ITER+CV_TERMCRIT_EPS,同时使max_iter和epsilon有效*/

CvTermCriteria cvCheckTermCriteria(CvTermCriteria criteria,double default_eps,int

default_max_iters);1CV_TERMCRIT_ITER2

此文档由OpenCV中文论坛会员HEYOUP翻译并整理

二 : STM32F205xx207xx参考手册

STM32F205xxSTM32F207xx

ARM-based 32-bit MCU, 150DMIPs, up to 1 MB Flash/128+4KB RAM,USB OTG HS/FS, Ethernet, 17 TIMs, 3 ADCs, 15 comm. interfaces & camera

Preliminary data

Features

■

■

■

■

■

■■

■

■

Core: ARM 32-bit Cortex?-M3 CPU with Adaptive real-time accelerator (ART

Accelerator?) allowing 0-wait state execution performance from Flash memory, frequency up to 120MHz, memory protection unit,

150DMIPS/1.25DMIPS/MHz (Dhrystone 2.1)Memories

–Up to 1 Mbyte of Flash memory–Up to 128 + 4 Kbytes of SRAM

–Flexible static memory controller that

supports Compact Flash, SRAM, PSRAM, NOR and NAND memories

–LCD parallel interface, 8080/6800 modesClock, reset and supply management

–1.8 to 3.6 V application supply and I/Os–POR, PDR, PVD and BOR–4 to 26 MHz crystal oscillator

–Internal 16MHz factory-trimmed RC (1% accuracy)

–32kHz oscillator for RTC with calibration–Internal 32kHz RC with calibrationLow power

–Sleep, Stop and Standby modes

–VBAT supply for RTC, 20 × 32 bit backup registers, and optional 4 KB backup SRAM3 × 12-bit, 0.5 μs A/D converters–up to 24 channels

–up to 6 MSPS in triple interleaved mode2 × 12-bit D/A convertersGeneral-purpose DMA

–16-stream DMA controller with centralized FIFOs and burst supportUp to 17 timers

–Up to twelve 16-bit and two 32-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder inputDebug mode

–Serial wire debug (SWD) & JTAG interfaces–Cortex-M3 Embedded Trace Macrocell?

1.Package not in production (for development only).■

■

■

■■■

Up to 140 I/O ports with interrupt capability:–Up to 136 fast I/Os up to 60MHz–Up to 138 5V-tolerant I/Os

Up to 15 communication interfaces

–Up to 3 × I2C interfaces (SMBus/PMBus)–Up to 4 USARTs and 2 UARTs (7.5 Mbit/s, ISO 7816 interface, LIN, IrDA, modem control)

–Up to 3 SPIs (30 Mbit/s), 2 with muxed I2S to achieve audio class accuracy via audio PLL or external PLL

–2 × CAN interfaces (2.0B Active)–SDIO interface

Advanced connectivity

–USB 2.0 full-speed device/host/OTG controller with on-chip PHY–USB 2.0 high-speed/full-speed

device/host/OTG controller with dedicated DMA, on-chip full-speed PHY and ULPI–10/100 Ethernet MAC with dedicated DMA: supports IEEE 1588v2 hardware, MII/RMII8- to 14-bit parallel camera interface: up to 27Mbyte/s at 27MHz or 48 Mbyte/s at 48 MHzCRC calculation unit, 96-bit unique IDAnalog true random number generator

Device summary

Part number

STM32F205RB, STM32F205RC, STM32F205RE, STM32F205RF, STM32F205RG, STM32F205VB, STM32F205VC, STM32F205VE, STM32F205VF STM32F205VG, STM32F205ZC, STM32F205ZE, STM32F205ZF, STM32F205ZG

STM32F207IC, STM32F207IE, STM32F207IF, STM32F207IG, STM32F207ZC, STM32F207ZE, STM32F207ZF, STM32F207ZG, STM32F207VC, STM32F207VE, STM32F207VF, STM32F207VG

Table 1.

Reference

STM32F205xx

STM32F207xx

November 2010Doc ID 15818 Rev 51/147

www.st.com

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

205 STM32F205xx207xx参考手册

ContentsSTM32F205xx, STM32F207xxContents

1

2Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.1

2.2Full compatibility throughout the family . . . . . . . . . . . . . . . . . . . . . . . . . . 13Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2.1

2.2.2

2.2.3

2.2.4

2.2.5

2.2.6

2.2.7

2.2.8

2.2.9

2.2.10

2.2.11

2.2.12

2.2.13

2.2.14

2.2.15

2.2.16

2.2.17

2.2.18

2.2.19

2.2.20

2.2.21

2.2.22

2.2.23

2.2.24

2.2.25

2.2.26

2.2.27

2.2.28ARM? Cortex?-M3 core with embedded Flash and SRAM . . . . . . . . . 16Memory protection unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16Adaptive real-time memory accelerator (ART Accelerator?) . . . . . . . . 16Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16CRC (cyclic redundancy check) calculation unit . . . . . . . . . . . . . . . . . . 17True random number generator (RNG) . . . . . . . . . . . . . . . . . . . . . . . . . 17Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Multi-AHB bus matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18FSMC (flexible static memory controller) . . . . . . . . . . . . . . . . . . . . . . . . 18Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . 19External interrupt/event controller (EXTI) . . . . . . . . . . . . . . . . . . . . . . . 19Clocks and startup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20Power supply schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20Real-time clock (RTC), backup SRAM and backup registers . . . . . . . . 23Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23VBAT operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24Basic timers TIM6 and TIM7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Independent watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Window watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26SysTick timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27I2C bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27Universal synchronous/asynchronous receiver transmitters(UARTs/USARTs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27Serial peripheral interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

2/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xx2.2.29

2.2.30

2.2.31

2.2.32

2.2.33

2.2.34

2.2.35

2.2.36

2.2.37

2.2.38

2.2.39

2.2.40

2.2.41

2.2.42ContentsInter-integrated sound (I2S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28SDIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28Ethernet MAC interface with dedicated DMA and IEEE1588 support . 29Controller area network (CAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29Universal serial bus on-the-go full-speed (OTG_FS) . . . . . . . . . . . . . . . 29Universal serial bus on-the-go high-speed (OTG_HS) . . . . . . . . . . . . . 30Audio PLL (PLLI2S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Digital camera interface (DCMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31GPIOs (general-purpose inputs/outputs) . . . . . . . . . . . . . . . . . . . . . . . . 31ADCs (analog-to-digital converters) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31DAC (digital-to-analog converter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Serial wire JTAG debug port (SWJ-DP) . . . . . . . . . . . . . . . . . . . . . . . . . 32Embedded Trace Macrocell? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3

4

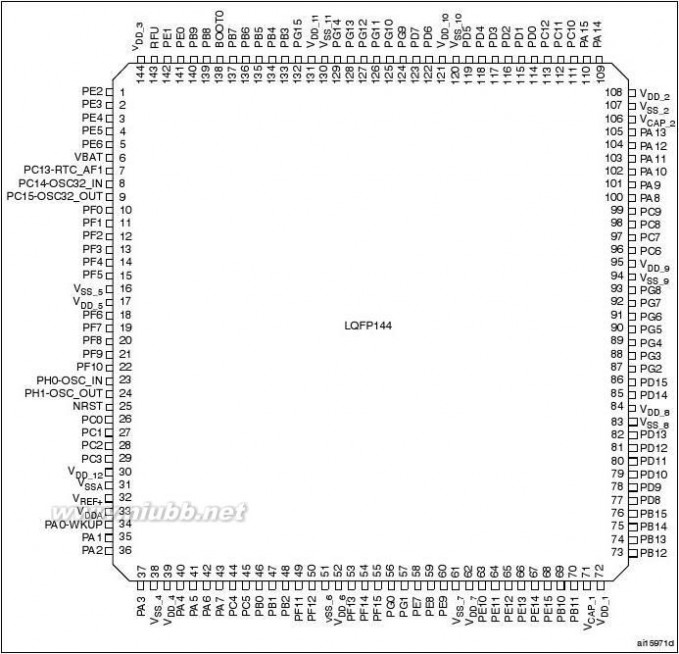

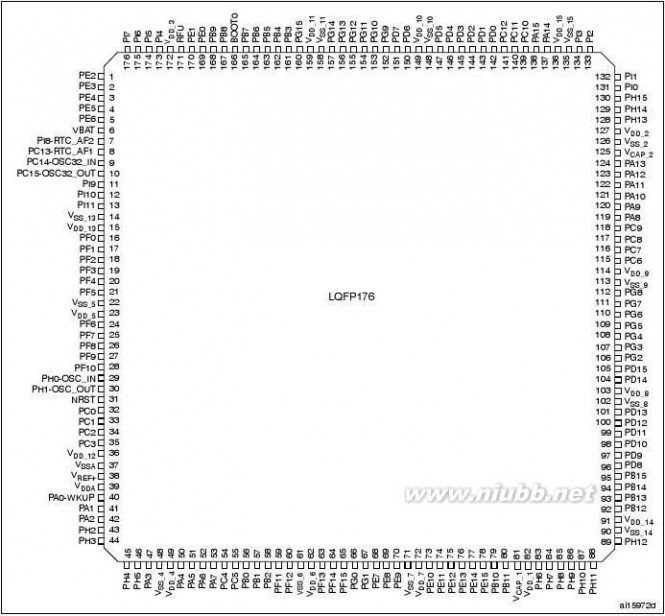

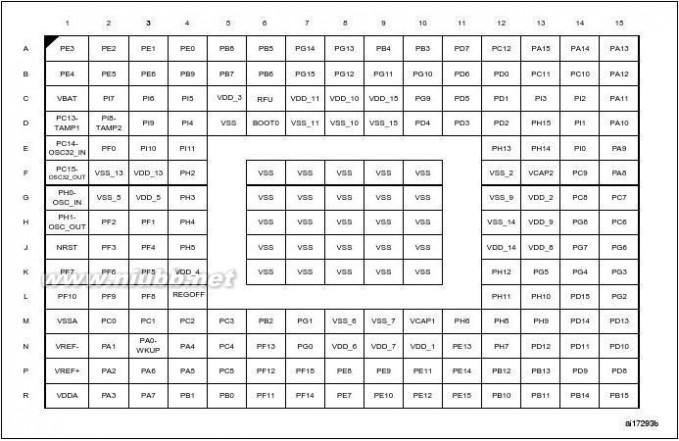

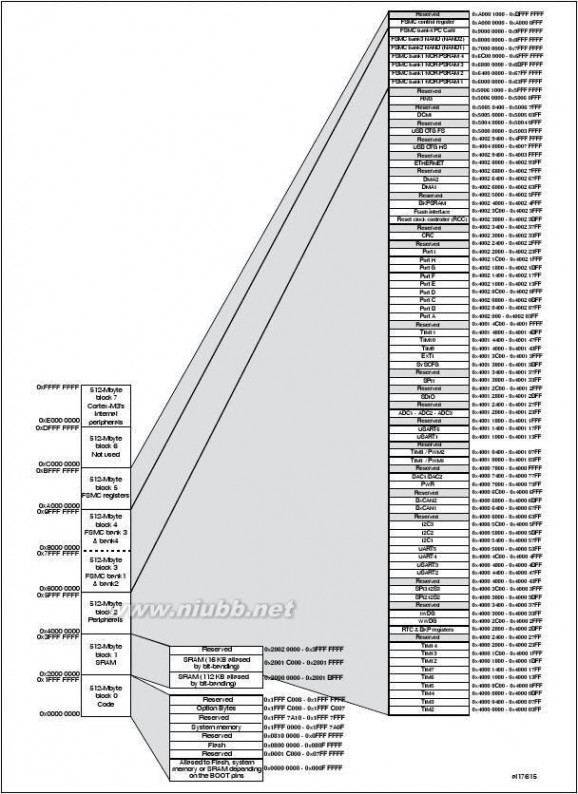

5Pinouts and pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5.1Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

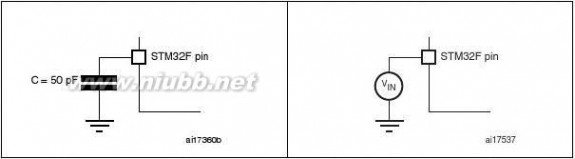

5.1.1

5.1.2

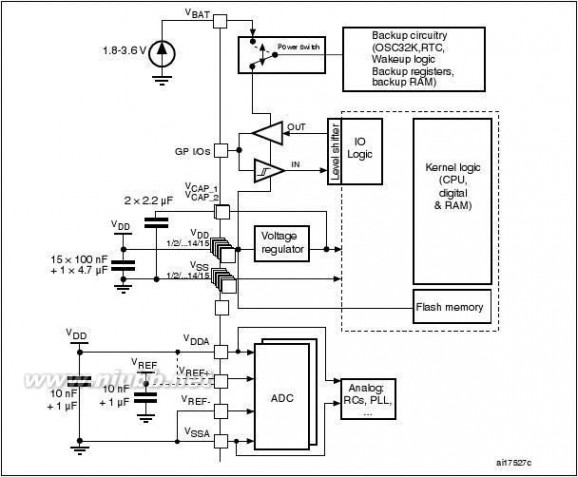

5.1.3

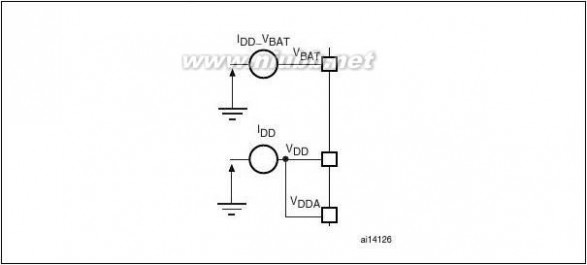

5.1.4

5.1.5

5.1.6

5.1.7Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.2

5.3Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.3.1

5.3.2

5.3.3

5.3.4

5.3.5

5.3.6General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57Operating conditions at power-up / power-down (regulator not bypassed) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59Operating conditions at power-up / power-down in regulatorbypass mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60Embedded reset and power control block characteristics . . . . . . . . . . . 60Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Doc ID 15818 Rev 53/147

205 STM32F205xx207xx参考手册

Contents5.3.7

5.3.8

5.3.9

5.3.10

5.3.11

5.3.12

5.3.13

5.3.14

5.3.15

5.3.16

5.3.17

5.3.18

5.3.19

5.3.20

5.3.21

5.3.22

5.3.23

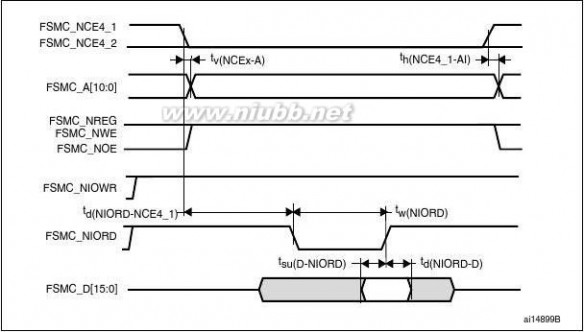

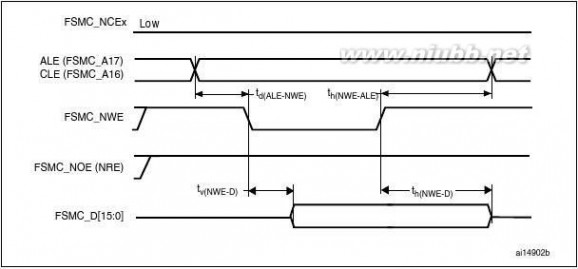

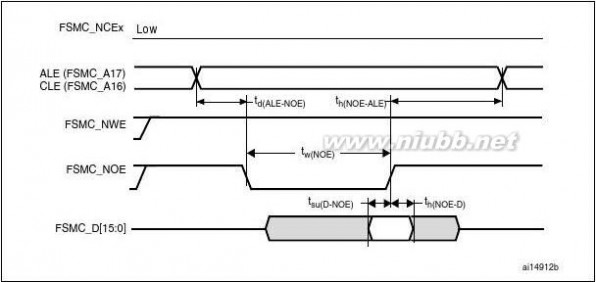

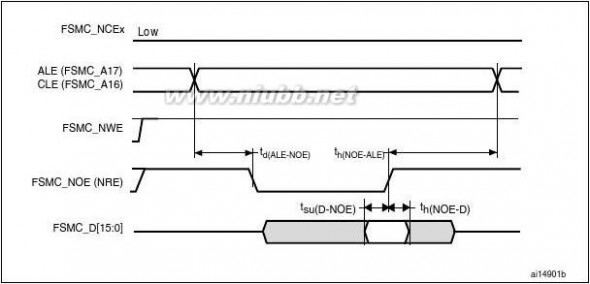

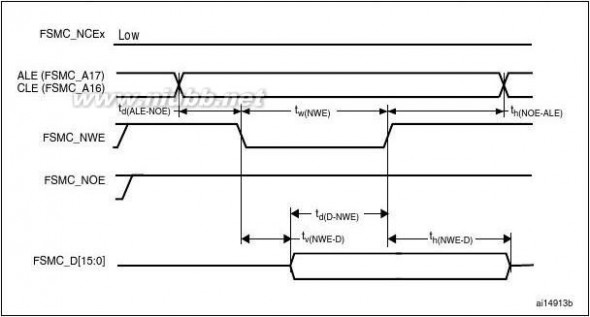

5.3.24

5.3.25

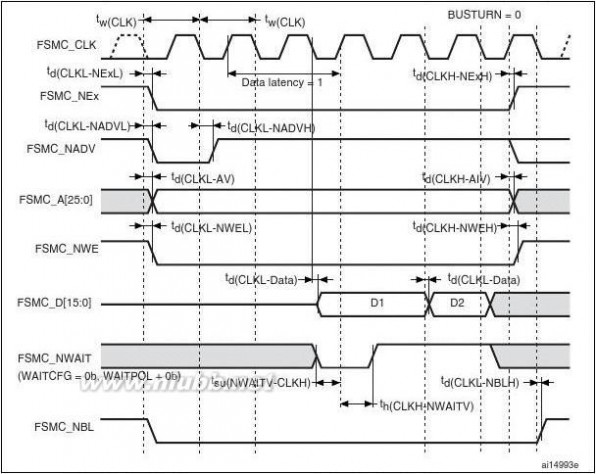

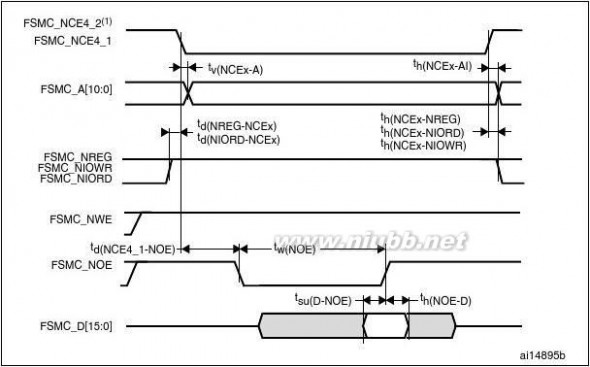

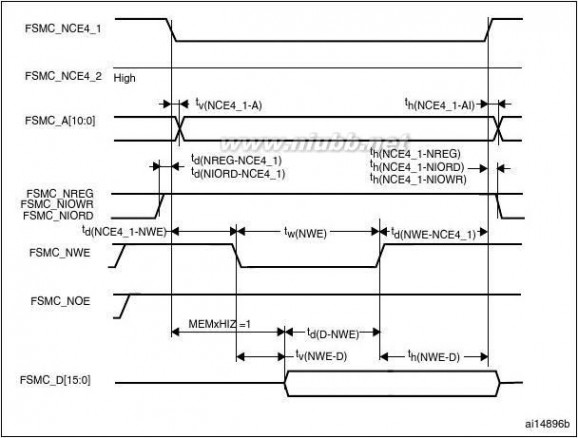

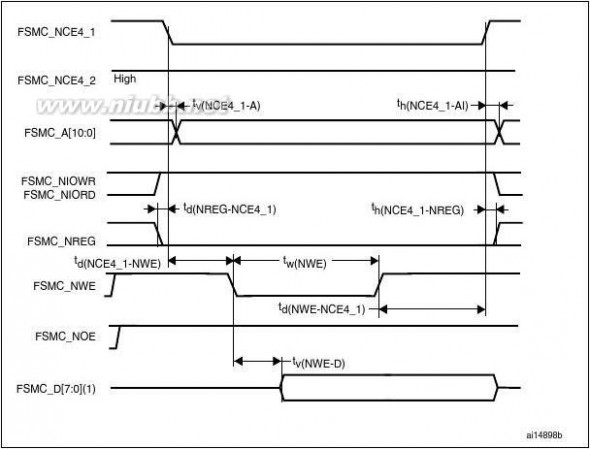

5.3.26STM32F205xx, STM32F207xxInternal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 71Wakeup time from low-power mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72PLL spread spectrum clock generation (SSCG) characteristics . . . . . . 73Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . . 77I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82TIM timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83Communications interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8512-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98DAC electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 104VBAT monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104FSMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105Camera interface (DCMI) timing specifications . . . . . . . . . . . . . . . . . . 123SD/SDIO MMC card host interface (SDIO) characteristics . . . . . . . . . 124RTC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

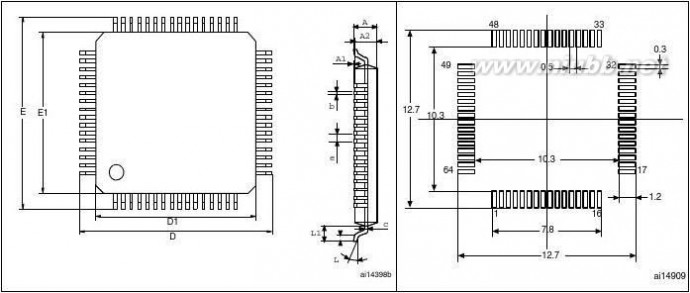

6Package characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

6.1

6.2Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

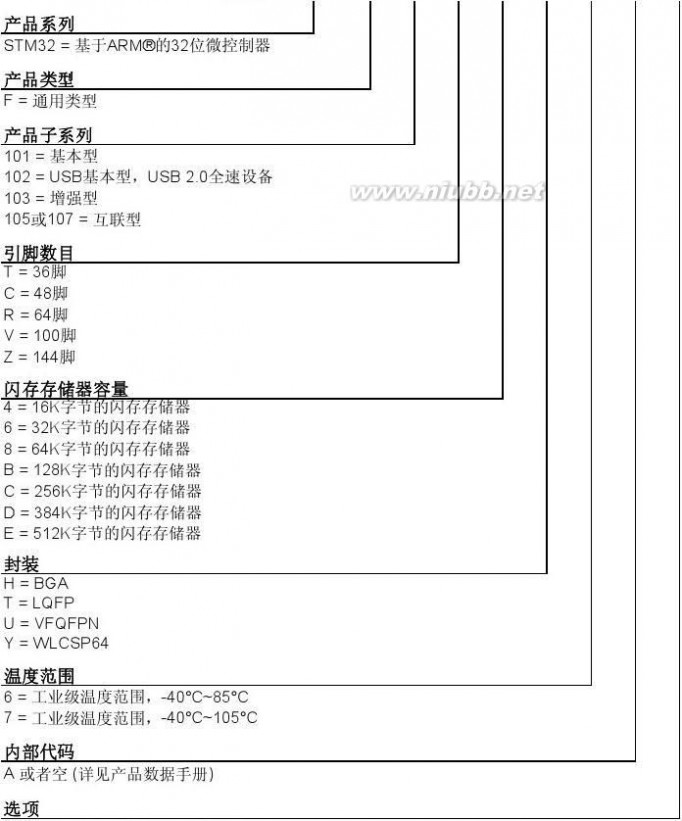

7Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134Appendix AApplication block diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

A.1

A.2

A.3

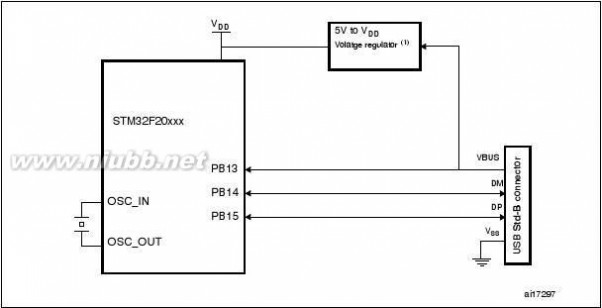

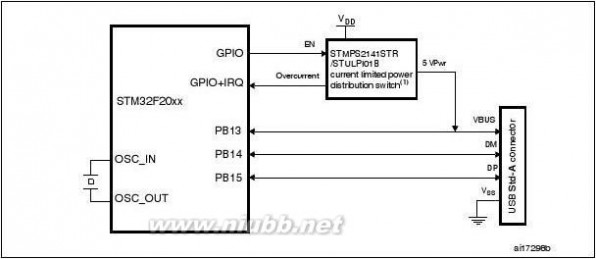

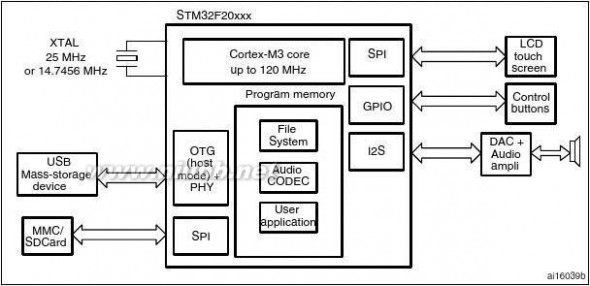

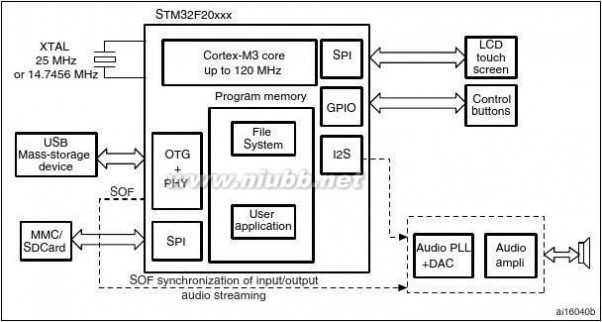

A.4

A.5Main applications versus package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135Application example with regulator off. . . . . . . . . . . . . . . . . . . . . . . . . . . 136USB OTG full speed (FS) interface solutions . . . . . . . . . . . . . . . . . . . . . 137USB OTG high speed (HS) interface solutions. . . . . . . . . . . . . . . . . . . . 138Complete audio player solutions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1434/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxList of tablesList of tables

Table 1.

Table 2.

Table 3.

Table 4.

Table 5.

Table 6.

Table 7.

Table 8.

Table 9.

Table 10.

Table 11.

Table 12.

Table 13.

Table 14.

Table 15.

Table 16.

Table 17.

Table 18.

Table 19.

Table 20.

Table 21.

Table 22.

Table 23.

Table 24.

Table 25.

Table 26.

Table 27.

Table 28.

Table 29.

Table 30.

Table 31.

Table 32.

Table 33.

Table 34.

Table 35.

Table 36.

Table 37.

Table 38.

Table 39.

Table 40.

Table 41.

Table 42.

Table 43.

Table 44.

Table 45.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1STM32F205xx and STM32F207xx features and peripheral counts . . . . . . . . . . . . . . . . . . 11Timer feature comparison. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24USART feature comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27STM32F20x pin and ball definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38Alternate function mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57Limitations depending on the operating power supply range. . . . . . . . . . . . . . . . . . . . . . . 58Operating conditions at power-up / power-down (regulator not bypassed) . . . . . . . . . . . . 59Operating conditions at power-up / power-down in regulator bypass mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60Embedded reset and power control block characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 60Typical and maximum current consumption in Run mode, code with data processingrunning from Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62Typical and maximum current consumption in Run mode, code with data processing running from RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63Typical and maximum current consumption in Sleep mode. . . . . . . . . . . . . . . . . . . . . . . . 63Typical and maximum current consumptions in Stop mode. . . . . . . . . . . . . . . . . . . . . . . . 64Typical and maximum current consumptions in Standby mode . . . . . . . . . . . . . . . . . . . . . 64Typical and maximum current consumptions in VBAT mode. . . . . . . . . . . . . . . . . . . . . . . 65Peripheral current consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65High-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67Low-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67HSE 4-26 MHz oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69LSE oscillator characteristics (fLSE = 32.768 kHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70HSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71LSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72Main PLL characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72PLLI2S (audio PLL) characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72SSCG parameters constraint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73Flash memory characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75Flash memory programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75Flash memory programming with VPP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75Flash memory endurance and data retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76EMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77ESD absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78Output voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80I/O AC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82Characteristics of TIMx connected to the APB1 domain . . . . . . . . . . . . . . . . . . . . . . . . . . 83Characteristics of TIMx connected to the APB2 domain . . . . . . . . . . . . . . . . . . . . . . . . . . 84

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

Doc ID 15818 Rev 55/147

205 STM32F205xx207xx参考手册

List of tablesTable 46.

Table 47.

Table 48.

Table 49.

Table 50.

Table 51.

Table 52.

Table 53.

Table 54.

Table 55.

Table 56.

Table 57.

Table 58.

Table 59.

Table 60.

Table 61.

Table 62.

Table 63.

Table 64.

Table 65.

Table 66.

Table 67.

Table 68.

Table 69.

Table 70.

Table 71.

Table 72.

Table 73.

Table 74.

Table 75.

Table 76.

Table 77.

Table 78.

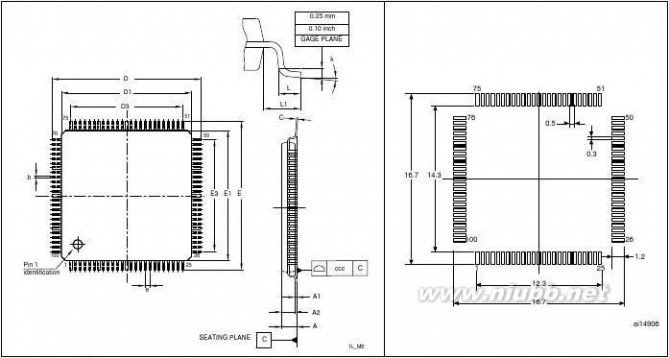

Table 79.

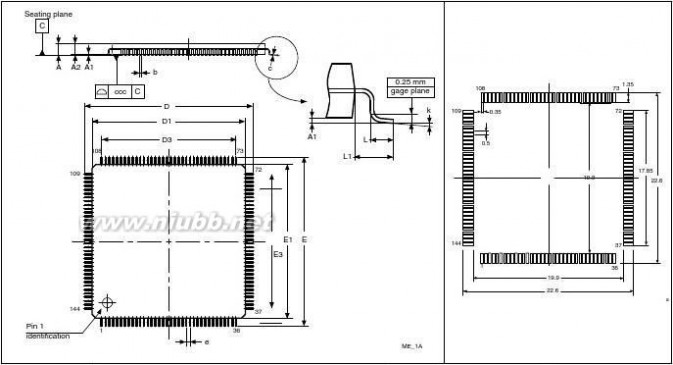

Table 80.

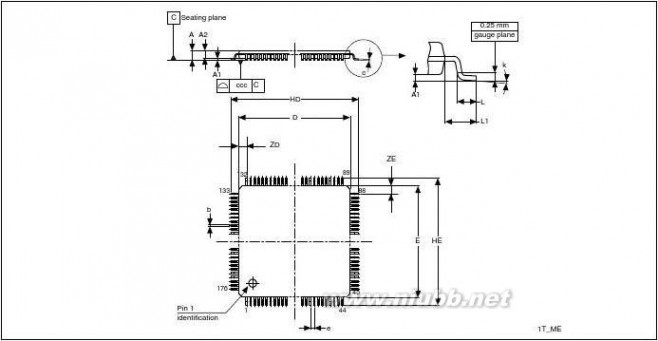

Table 81.

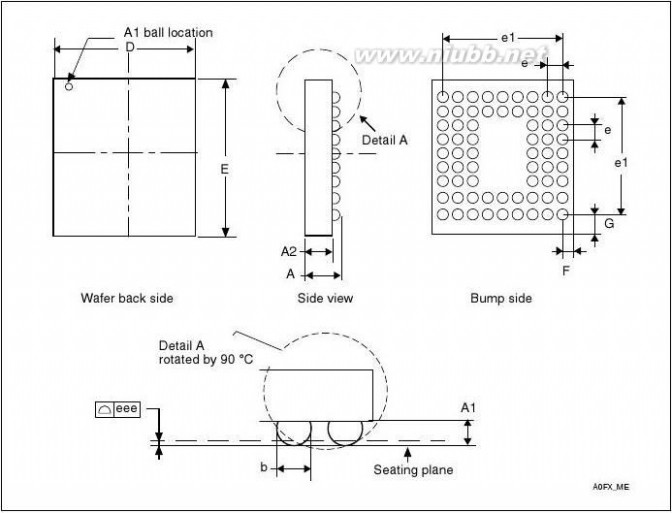

Table 82.

Table 83.

Table 84.

Table 85.

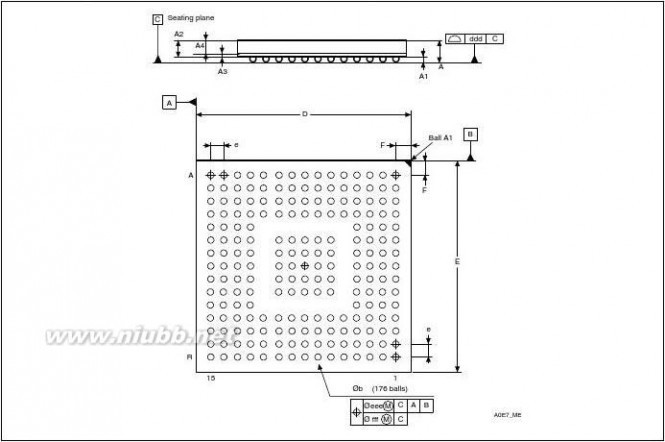

Table 86.

Table 87.STM32F205xx, STM32F207xxI2C characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85SCL frequency (fPCLK1= 30 MHz.,VDD = 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86SPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87I2S characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90USB OTG FS startup time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92USB OTG FS DC electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92USB OTG FS electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94Clock timing parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94ULPI timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95Ethernet DC electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95Dynamics characteristics: Ethernet MAC signals for SMI. . . . . . . . . . . . . . . . . . . . . . . . . . 96Dynamics characteristics: Ethernet MAC signals for RMII . . . . . . . . . . . . . . . . . . . . . . . . . 96Dynamics characteristics: Ethernet MAC signals for MII . . . . . . . . . . . . . . . . . . . . . . . . . . 97ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98ADC accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102TS characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104VBAT monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104Embedded internal reference voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings . . . . . . . . . . . . . . . . . 106Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings . . . . . . . . . . . . . . . . . 107Asynchronous multiplexed PSRAM/NOR read timings. . . . . . . . . . . . . . . . . . . . . . . . . . . 108Asynchronous multiplexed PSRAM/NOR write timings . . . . . . . . . . . . . . . . . . . . . . . . . . 109Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 111Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113Synchronous non-multiplexed NOR/PSRAM read timings. . . . . . . . . . . . . . . . . . . . . . . . 114Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115Switching characteristics for PC Card/CF read and write cycles . . . . . . . . . . . . . . . . . . . 120Switching characteristics for NAND Flash read and write cycles . . . . . . . . . . . . . . . . . . . 123DCMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123SD / MMC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124RTC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data. . . . . . . . . 127WLCSP64+2 - 0.400 mm pitch wafer level chip size package mechanical data . . . . . . . 128LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package mechanical data. . . . . . . 129LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data . . . . . . . 130LQFP176 - Low profile quad flat package 24 × 24 × 1.4 mm package mechanical data . 131UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data . 132Package thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133Ordering information scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134Main applications versus package for STM32F207xx microcontrollers . . . . . . . . . . . . . . 135Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1436/147Doc ID 15818 Rev 5

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxList of figuresList of figures

Figure 1.

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

Figure 15.

Figure 16.

Figure 17.

Figure 18.

Figure 19.

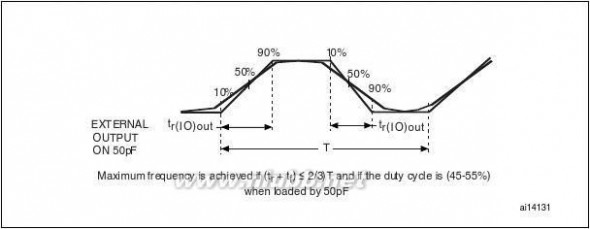

Figure 20.

Figure 21.

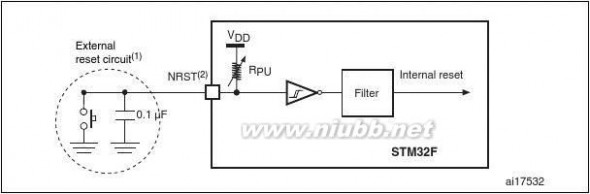

Figure 22.

Figure 23.

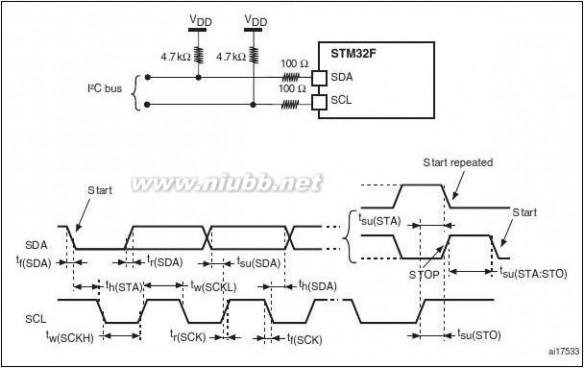

Figure 24.

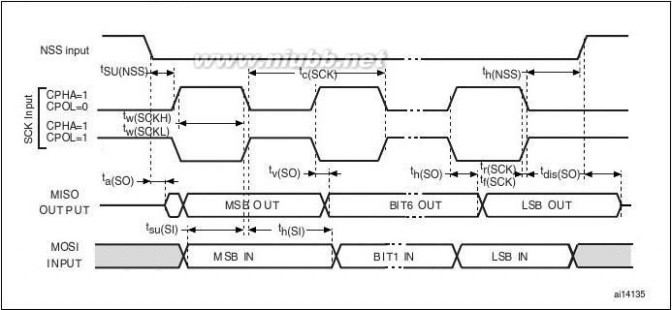

Figure 25.

Figure 26.

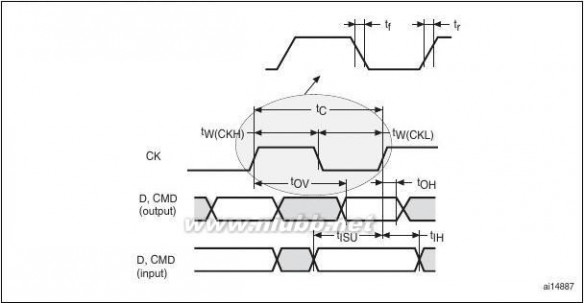

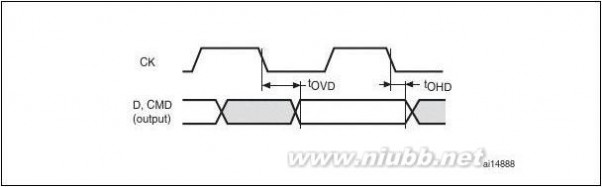

Figure 27.

Figure 28.

Figure 29.

Figure 30.

Figure 31.

Figure 32.

Figure 33.

Figure 34.

Figure 35.

Figure 36.

Figure 37.

Figure 38.

Figure 39.

Figure 40.

Figure 41.

Figure 42.

Figure 43.

Figure 44.

Figure 45.

Figure 46.Compatible board design: LQFP144 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Compatible board design: LQFP100 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14Compatible board design: LQFP64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14STM32F20x block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15Multi-AHB matrix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Startup in regulator bypass/regulator off mode: slow VDD slope - power-down reset risen after VCAP_1/VCAP_2 stabilization. . . . . . . . . . . . . . . . . . . . . . . . 22Startup in regulator bypass/regulator off mode: slow VDD slope - power-down reset risen before VCAP_1/VCAP_2 stabilization . . . . . . . . . . . . . . . . . . . . . . 22Sartup in regulator bypass/regulator off and internal reset off . . . . . . . . . . . . . . . . . . . . . . 22STM32F20x LQFP64 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33STM32F20x WLCSP64+2 ballout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33STM32F20x LQFP100 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34STM32F20x LQFP144 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35STM32F20x LQFP176 pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36STM32F21xxx UFBGA176 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37Memory map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Pin input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55Number of wait states versus fCPU and VDD range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68Typical application with an 8 MHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69Typical application with a 32.768 kHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70PLL output clock waveforms in center spread mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74PLL output clock waveforms in down spread mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74I/O AC characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83I2C bus AC waveforms and measurement circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88SPI timing diagram - slave mode and CPHA = 1(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88SPI timing diagram - master mode(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89I2S slave timing diagram (Philips protocol)(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91I2S master timing diagram (Philips protocol)(1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91USB OTG FS timings: definition of data signal rise and fall time . . . . . . . . . . . . . . . . . . . . 93ULPI timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95Ethernet SMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96Ethernet RMII timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96Ethernet MII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97ADC accuracy characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100Power supply and reference decoupling (VREF+ not connected to VDDA). . . . . . . . . . . . . 101Power supply and reference decoupling (VREF+ connected to VDDA). . . . . . . . . . . . . . . . 10112-bit buffered /non-buffered DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms . . . . . . . . . . . . . . 105Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms . . . . . . . . . . . . . . 106

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

Doc ID 15818 Rev 57/147

205 STM32F205xx207xx参考手册

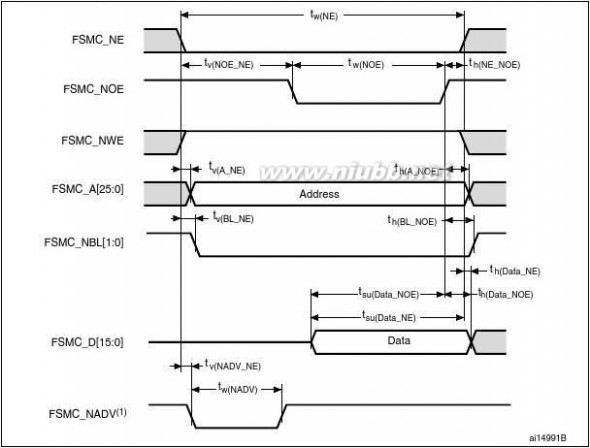

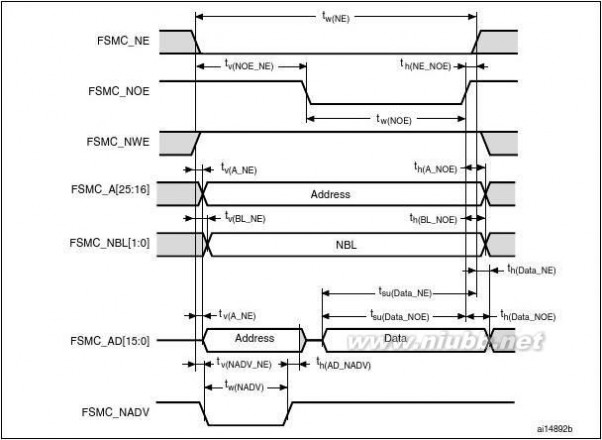

List of figuresFigure 47.

Figure 48.

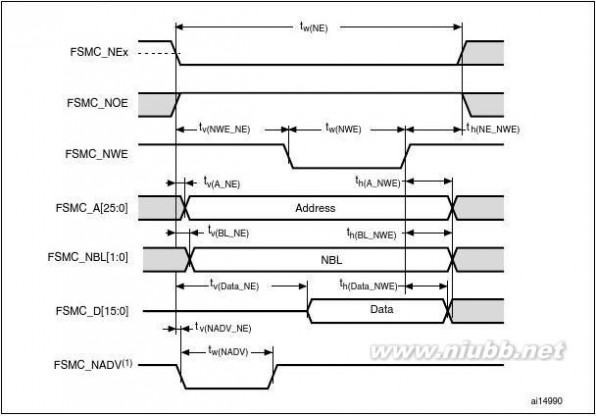

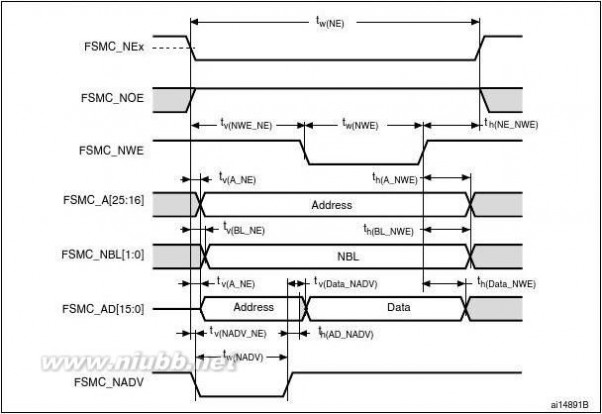

Figure 49.

Figure 50.

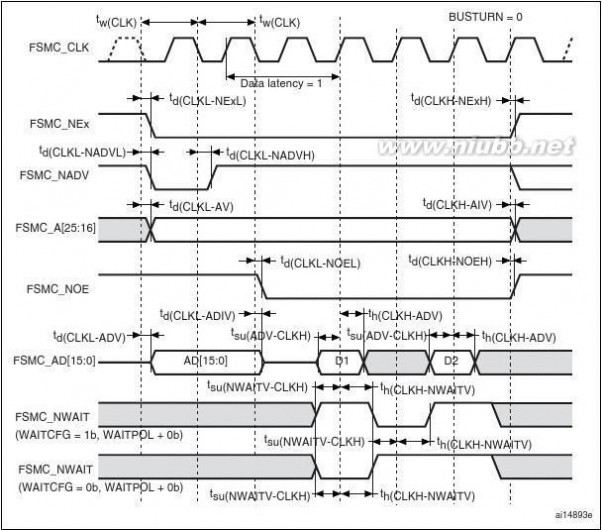

Figure 51.

Figure 52.

Figure 53.

Figure 54.

Figure 55.

Figure 56.

Figure 57.

Figure 58.

Figure 59.

Figure 60.

Figure 61.

Figure 62.

Figure 63.

Figure 64.

Figure 65.

Figure 66.

Figure 67.

Figure 68.

Figure 69.

Figure 70.

Figure 71.

Figure 72.

Figure 73.

Figure 74.

Figure 75.

Figure 76.

Figure 77.

Figure 78.

Figure 79.

Figure 80.

Figure 81.

Figure 82.

Figure 83.

Figure 84.

Figure 85.

Figure 86.

Figure 87.STM32F205xx, STM32F207xxAsynchronous multiplexed PSRAM/NOR read waveforms. . . . . . . . . . . . . . . . . . . . . . . . 107Asynchronous multiplexed PSRAM/NOR write waveforms . . . . . . . . . . . . . . . . . . . . . . . 109Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 110Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112Synchronous non-multiplexed NOR/PSRAM read timings. . . . . . . . . . . . . . . . . . . . . . . . 114Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115PC Card/CompactFlash controller waveforms for common memory read access. . . . . . 116PC Card/CompactFlash controller waveforms for common memory write access. . . . . . 117PC Card/CompactFlash controller waveforms for attribute memory readaccess. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118PC Card/CompactFlash controller waveforms for attribute memory writeaccess. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119PC Card/CompactFlash controller waveforms for I/O space read access . . . . . . . . . . . . 119PC Card/CompactFlash controller waveforms for I/O space write access. . . . . . . . . . . . 120NAND controller waveforms for read access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122NAND controller waveforms for write access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122NAND controller waveforms for common memory read access. . . . . . . . . . . . . . . . . . . . 122NAND controller waveforms for common memory write access. . . . . . . . . . . . . . . . . . . . 123SDIO high-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124SD default mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline . . . . . . . . . . . . . . . . 127Recommended footprint(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127WLCSP64+2 - 0.400 mm pitch wafer level chip size package outline . . . . . . . . . . . . . . . 128LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline . . . . . . . . . . . . . . . 129Recommended footprint(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129LQFP144, 20 x 20 mm, 144-pin low-profile quadflat package outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130Recommended footprint(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130LQFP176 - Low profile quad flat package 24 × 24 × 1.4 mm, package outline . . . . . . . . 131UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm, package outline . 132Regulator bypass/regulator off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136Regulator bypass/regulator off and internal reset off . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136USB OTG FS peripheral-only connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137USB OTG FS host-only connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137OTG FS connection dual-role with internal PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138USB OTG HS peripheral-only connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138USB OTG HS host-only connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139OTG HS connection dual-role with external PHY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139Complete audio player solution 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140Complete audio player solution 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140Audio player solution using PLL, PLLI2S, USB and 1 crystal. . . . . . . . . . . . . . . . . . . . . . 141Audio PLL (PLLI2S) providing accurate I2S clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141Master clock (MCK) used to drive the external audio DAC. . . . . . . . . . . . . . . . . . . . . . . . 142Master clock (MCK) not used to drive the external audio DAC. . . . . . . . . . . . . . . . . . . . . 1428/147Doc ID 15818 Rev 5

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxIntroduction1 Introduction

This datasheet provides the description of the STM32F205xx and STM32F207xx lines of

microcontrollers. For more details on the whole STMicroelectronics STM32? family, please

refer to Section2.1: Full compatibility throughout the family.

The STM32F205xx and STM32F207xx datasheet should be read in conjunction with the

STM32F20x/STM32F21x reference manual.

For information on programming, erasing and protection of the internal Flash memory,

please refer to the STM32F20x/STM32F21x Flash programming manual.

The reference and Flash programming manuals are both available from the

STMicroelectronics website www.st.com.

For information on the Cortex?-M3 core please refer to the Cortex?-M3 Technical

Reference Manual, available from the www.arm.com website at the following address:

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/.

Doc ID 15818 Rev 59/147

205 STM32F205xx207xx参考手册

DescriptionSTM32F205xx, STM32F207xx2 Description

The STM32F205xx and STM32F207xx family is based on the high-performance ARM?

Cortex?-M3 32-bit RISC core operating at a frequency of up to 120 MHz. The family

incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to

128Kbytes of system SRAM), up to 4Kbytes of backup SRAM, and an extensive range of

enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit

multi-AHB bus matrix.

The devices also feature an adaptive real-time memory accelerator (ART Accelerator?)

which allows to achieve a performance equivalent to 0 wait state program execution from

Flash memory at a CPU frequency up to 120MHz. This performance has been validated

using the CoreMark benchmark.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose

16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers.

a true number random generator (RNG). They also feature standard and advanced

communication interfaces. New advanced peripherals include an SDIO, an enhanced

flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins

and more), and a camera interface for CMOS sensors.

●

●Up to three I2CsThree SPIs, two I2Ss. To achieve audio class accuracy, the I2S peripherals can be

clocked via a dedicated internal audio PLL or via an external PLL to allow

synchronization.

4 USARTs and 2 UARTs

An USB OTG full-speed and a USB OTG full-speed with high-speed capability (with the ULPI),

Two CANs

An SDIO interface

Ethernet and the camera interface available on STM32F207xx devices only.●●●●●

The STM32F205xx and STM32F207xx family operates in the –40 to +105°C temperature

range from a 1.8V to 3.6V power supply. A comprehensive set of power-saving mode

allows the design of low-power applications.

The STM32F205xx and STM32F207xx family offers devices in four packages ranging from

64 pins to 176 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F205xx and STM32F207xx microcontroller family suitable

for a wide range of applications:

●

●

●

●

●

●Motor drive and application controlMedical equipmentIndustrial applications: PLC, inverters, circuit breakersPrinters, and scannersAlarm systems, video intercom, and HVACHome audio appliances

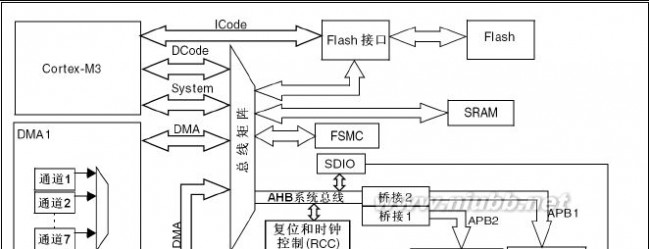

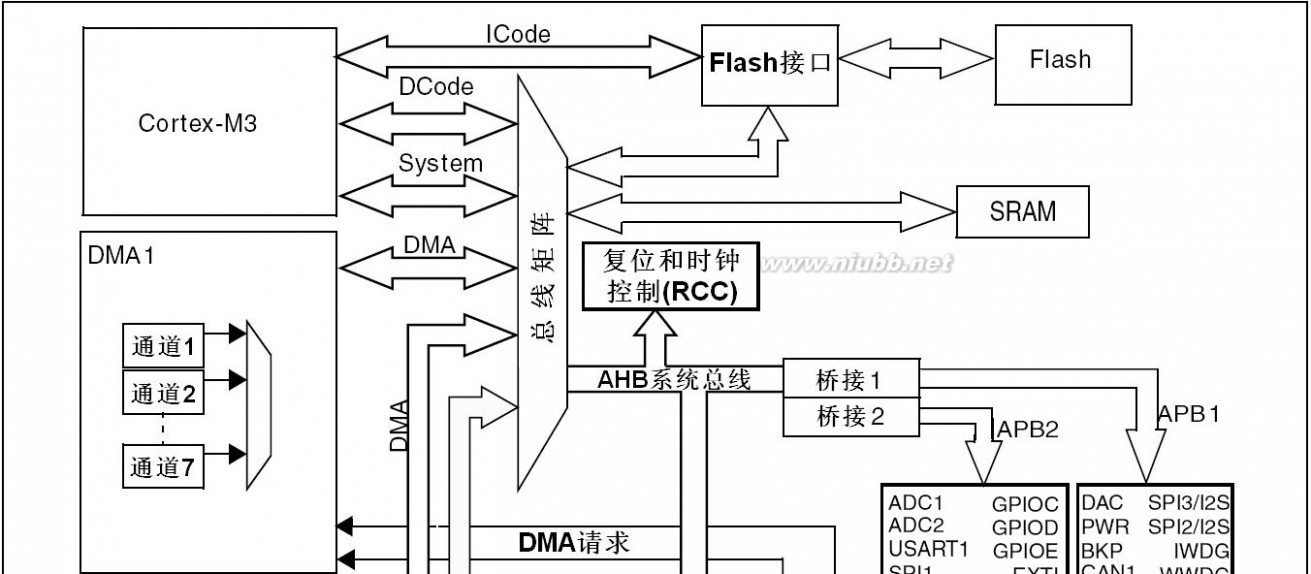

Figure4 shows the general block diagram of the device family.

10/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

Table 2.STM32F205xx and STM32F207xx features and peripheral counts

PeripheralsSTM32F205RxSTM32F205VxSTM32F205ZxSTM32F207VxSTM32F207ZxSTM32F207IxFlash memory in

Kbytes128256512768102412825651276810242565127681024256512768102425651276810242565127681024SRAM in System6496649696

Kbytes(48+16)(80+16)128(112+16)(48+16)(80+16)128 (112+16)(80+16)128 (112+16)128 (112+16)

Backup4444

FSMC memory

controllerNoYes

EthernetNoYes

General-

purpose10

TimersAdvanced

-control2

Doc ID 15818 Rev 5Basic2

Random number

generatorYes

SPI / (I2S)3 (2)

IC3

USART4

Comm. UART2

interfacesUSB OTG

FS

USB OTG 1HS/FS1FS, 1HS/FS

HS

CAN2

Camera interfaceNoYes

GPIOs51821148211414012-bit ADC3

Number of channels16162416242412-bit DACYes

Number of channels2

11/147STM32F205xx, STM32F207xxDescription

205 STM32F205xx207xx参考手册

12/147Table 2.STM32F205xx and STM32F207xx features and peripheral counts (continued)

PeripheralsSTM32F205RxSTM32F205VxSTM32F205ZxSTM32F207VxSTM32F207ZxSTM32F207IxMaximum CPU

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

frequency 120 MHz

Operating voltage 1.8 V to 3.6 V

Operating Ambient temperatures: –40 to +85 °C /–40 to +105 °C

temperaturesJunction temperature: –40 to + 125 °C

LQFP64PackageWLCSP64+2LQFP100LQFP144LQFP100LQFP144LQFP176

UFBGA176

1.Package not in production and available for development only.

Doc ID 15818 Rev 5DescriptionSTM32F205xx, STM32F207xx

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

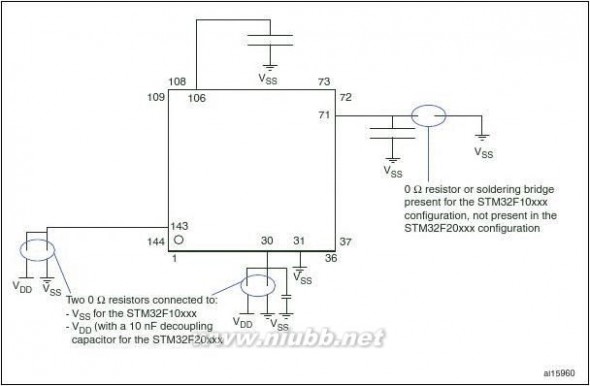

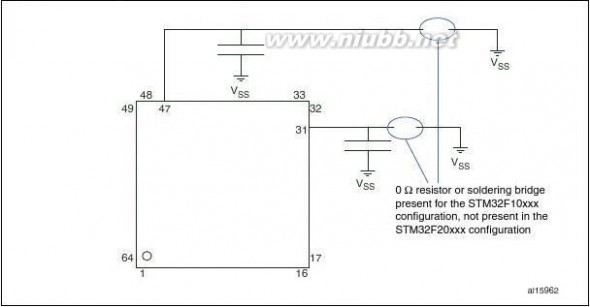

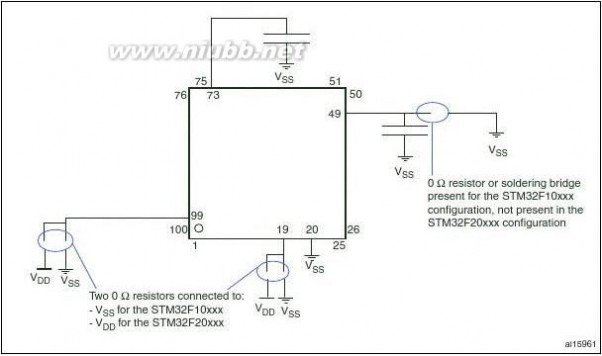

2.1 Full compatibility throughout the family

The STM32F205xx and STM32F207xx constitute the STM32F20x family whose members

are fully pin-to-pin, software and feature compatible, allowing the user to try different

memory densities and peripherals for a greater degree of freedom during the development

cycle.

The STM32F205xx and STM32F207xx devices maintain a close compatibility with the

whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The

STM32F205xx and STM32F207xx, however, are not drop-in replacements for the

STM32F10xxx devices: the two families do not have the same power scheme, and so their

power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F20x

family remains simple as only a few pins are impacted.

Figure1 compatible board design between the STM32F20x and the STM32F10xxx family.

Doc ID 15818 Rev 513/147

205 STM32F205xx207xx参考手册

Description

STM32F205xx, STM32F207xx14/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

2.2 Device overview

Doc ID 15818 Rev 515/147

205 STM32F205xx207xx参考手册

DescriptionSTM32F205xx, STM32F207xx2.2.1 ARM? Cortex?-M3 core with embedded Flash and SRAM

The ARM Cortex-M3 processor is the latest generation of ARM processors for embedded

systems. It was developed to provide a low-cost platform that meets the needs of MCU

implementation, with a reduced pin count and low-power consumption, while delivering

outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M3 32-bit RISC processor features exceptional code-efficiency, delivering

the high-performance expected from an ARM core in the memory size usually associated

with 8- and 16-bit devices.

With its embedded ARM core, the STM32F205xx and STM32F207xx family is compatible

with all ARM tools and software.

Figure 1 shows the general block diagram of the STM32F20x family.

2.2.2 Memory protection unit

The memory protection unit (MPU) is used to separate the processing of tasks from the data

protection. The MPU can manage up to 8 protection areas that can all be further divided up

into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes

of addressable memory.

The memory protection unit is especially helpful for applications where some critical or

certified code has to be protected against the misbehavior of other tasks. It is usually

managed by an RTOS (real-time operating system). If a program accesses a memory

location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS

environment, the kernel can dynamically update the MPU area setting, based on the

process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

2.2.3 Adaptive real-time memory accelerator (ART Accelerator?)

The ART Accelerator? is a memory accelerator which is optimized for STM32 industry-

standard ARM? Cortex?-M3 processors. It balances the inherent performance advantage

of the ARM Cortex-M3 over Flash memory technologies, which normally requires the

processor to wait for the Flash memory at higher operating frequencies.

To release the processor full 150 DMIPS performance at this frequency, the accelerator

implements an instruction prefetch queue and branch cache which increases program

execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the

performance achieved thanks to the ART accelerator is equivalent to 0 wait state program

execution from Flash memory at a CPU frequency up to 120MHz.

2.2.4 Embedded Flash memory

The STM32F20x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes,

512 Kbytes, 768 Kbytes or 1 Mbytes available for storing programs and data.

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

16/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

2.2.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

2.2.6 True random number generator (RNG)

All STM32F2xxx products embed a true RNG that delivers 32-bit random numbers

produced by an integrated analog circuit.

2.2.7 Embedded SRAM

All STM32F20x products embed up to 128 Kbytes of system SRAM accessed (read/write) at

CPU clock speed with 0 wait states, plus 4 Kbytes of backup SRAM.

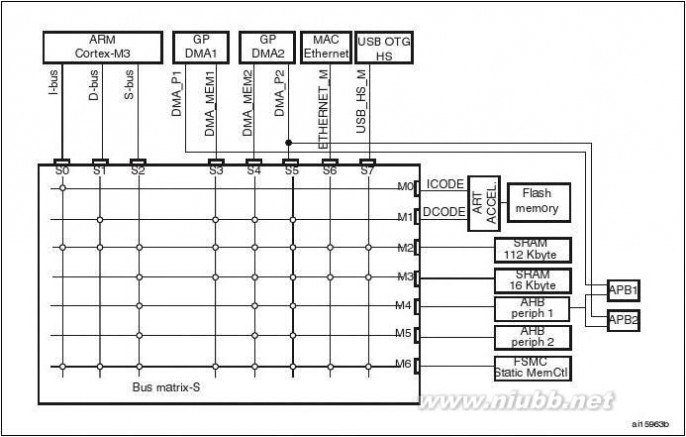

2.2.8 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

Doc ID 15818 Rev 517/147

205 STM32F205xx207xx参考手册

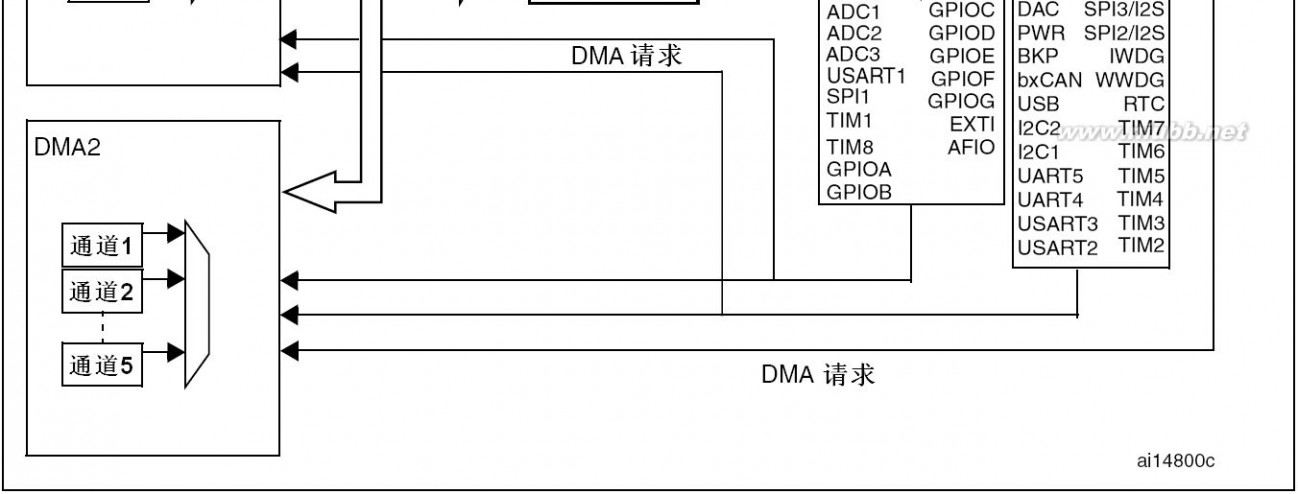

DescriptionSTM32F205xx, STM32F207xx2.2.9 DMA

The flexible 16-stream general-purpose DMAs (8 streams for DMA1 and 8 streams for

DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-to-

peripheral transfers. They share some centralized FIFOs for APB/AHB peripherals, support

burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB)

and performance.

The two DMA controllers support circular buffer management, so that no specific code is

needed when the controller reaches the end of the buffer. The two DMA controllers also

have a double buffering feature, which automates the use and switching of two memory

buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software

trigger on each stream. Configuration is made by software and transfer sizes between

source and destination are independent.

The DMA can be used with the main peripherals:

●

●

●

●

●

●

●

●SPI and I2SI2CUSART and UARTGeneral-purpose, basic and advanced-control timers TIMxDACSDIOCamera interface (DCMI)ADC.

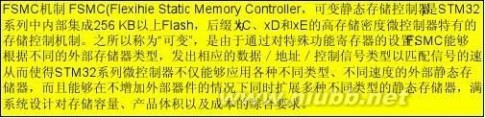

2.2.10 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F205xx and STM32F207xx family. It has four Chip

Select outputs supporting the following modes: PCCard/Compact Flash, SRAM, PSRAM,

NOR Flash and NAND Flash.

Functionality overview:

●

●

●Write FIFOCode execution from external memory except for NAND Flash and PC CardThe targeted frequency, fCLK, is equal to HCLK/2, so external access is at 60 MHz

when HCLK is at 120 MHz and external access is at 30 MHz when HCLK is at 60 MHz

LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It

supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to

specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-

effective graphic applications using LCD modules with embedded controllers or high

performance solutions using external controllers with dedicated acceleration.

18/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

2.2.11 Nested vectored interrupt controller (NVIC)

The STM32F205xx and STM32F207xx embed a nested vectored interrupt controller able to

handle up to 87 maskable interrupt channels (not including the 16 interrupt lines of the

Cortex?-M3) and 16 priority levels.

●

●

●

●

●

●

●

●Closely coupled NVIC gives low-latency interrupt processingInterrupt entry vector table address passed directly to the coreClosely coupled NVIC core interfaceAllows early processing of interruptsProcessing of late arriving, higher-priority interruptsSupport tail chainingProcessor state automatically savedInterrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt

latency.

2.2.12 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge-detector lines used to generate

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

interrupt/event requests. Each line can be independently configured to select the trigger

event (rising edge, falling edge, both) and can be masked independently. A pending register

maintains the status of the interrupt requests. The EXTI can detect an external line with a

pulse width shorter than the Internal APB2 clock period. Up to 140 GPIOs can be connected

to the 16 external interrupt lines.

2.2.13 Clocks and startup

System clock selection is performed on startup, however, the 16 MHz internal RC oscillator

is selected as the default CPU clock on reset. An external 4-26 MHz clock can be selected,

in which case it is monitored for failure. If failure is detected, the system automatically

switches back to the internal RC oscillator. A software interrupt is generated if enabled.

Similarly, full interrupt management of the PLL clock entry is available when necessary (for

example if an indirectly used external oscillator fails).

The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy over the full

temperature range.

The advanced clock controller clocks the core and all peripherals using a single crystal or

oscillator. In particular, the ethernet and USB OTG FS peripherals can be clocked by the

system clock.

Several prescalers and PLLs allow the configuration of the two AHB buses, the high-speed

APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two

AHB buses is 120MHz and the maximum frequency the high-speed APB domains is

60MHz. The maximum allowed frequency of the low-speed APB domain is 30MHz.

In order to achieve audio class performance, a specific crystal can be used. In this case, the

I2S master clock can generate all standard sampling frequencies from 8kHz to 96kHz.

Doc ID 15818 Rev 519/147

205 STM32F205xx207xx参考手册

DescriptionSTM32F205xx, STM32F207xx2.2.14 Boot modes

At startup, boot pins are used to select one out of three boot options:

●

●

●Boot from user Flashboot from system memoryBoot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by

using USART1 (PA9/PA10), USART3 (PC10/PC11 or PB10/PB11), CAN2 (PB5/PB6), USB

OTG FS in Device mode (PA9/PA11/PA12) through DFU (device firmware upgrade).

2.2.15 Power supply schemes

●VDD = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when

enabled), provided externally through VDD pins. On WLCSP package, VDD ranges from

1.65 to 3.6V.

VSSA, VDDA = 1.8 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks,

RCs and PLL. VDDA and VSSA must be connected to VDD and VSS, respectively.

VBAT = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup

registers (through power switch) when VDD is not present.●●

2.2.16 Power supply supervisor

The device has an integrated power-on reset (POR) / power-down reset (PDR) circuitry

coupled with a Brownout reset (BOR) circuitry. At power-on, BOR is always active, and

ensures proper operation starting from 1.8V. After the 1.8V BOR threshold is reached, the

option byte loading process starts, either to confirm or modify default thresholds, or to

disable BOR permanently. Three BOR thresholds are available through option bytes.

The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR or

VBOR, without the need for an external reset circuit. On devices in WLCSP package, BOR

can be inactivated by setting IRROFF to VDD (see Section2.2.17: Voltage regulator).

The device also features an embedded programmable voltage detector (PVD) that monitors

the VDD/VDDA power supply and compares it to the VPVD threshold. An interrupt can be

generated when VDD/VDDA drops below the VPVD threshold and/or when VDD/VDDA is higher

than the VPVD threshold. The interrupt service routine can then generate a warning

message and/or put the MCU into a safe state. The PVD is enabled by software.

2.2.17 Voltage regulator

The regulator has five operating modes:

●Regulator on

–

–

–Main regulator mode (MR)Low power regulator (LPR)Power-down

Regulator bypass/regulator off

Regulator bypass/regulator off and internal reset off●Regulator off––

20/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

Regulator on

These modes are activated by default on LQFP packages. On WLCPS66 and UFBGA176,

they are activated by setting REGOFF pin to VSS. VDD minimum value is 1.8V.

There are three regulator on modes:

●

●

●MR is used in the nominal regulation mode (Run)LPR is used in the Stop modes7Power-down is used in Standby mode:

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

The regulator output is in high impedance: the kernel circuitry is powered down,

inducing zero consumption (but the contents of the registers and SRAM are lost).

Regulator off

●Regulator bypass/regulator off

This mode is activated by setting REGOFF pin to VDD. It is available only on the

UFBGA and WLCSP packages.

The regulator bypass/regulator off mode allows to supply externally a 1.2V voltage

source through VCAP_1 and VCAP_2 pins, in addition to VDD.

VDD minimum value is 1.8V.

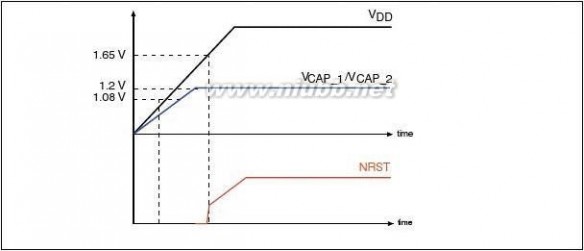

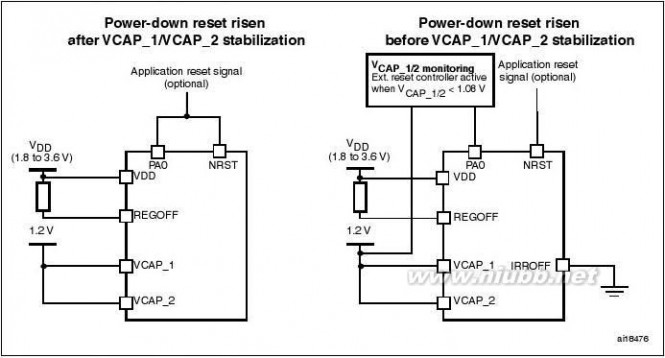

The following conditions must be respected in Regulator bypass mode:

–

–VDD should always be higher than VCAP_1 and VCAP_2 to avoid current injection between power domains. If the time for VCAP_1 and VCAP_2 to reach 1.08V is faster than the time for VDD to

reach 1.8V, then PA0 should be connected to the NRST pin (see Figure6).

Otherwise, PA0 should be asserted low externally until VDD reaches 1.8V (see

Figure7).

In regulator bypass only mode, PA0 cannot be used as a GPIO pin.

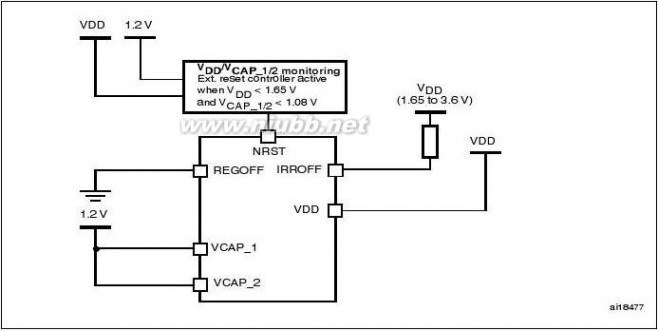

●Regulator bypass/regulator off and internal reset off

This mode is activated by setting IRROFF pin to VDD. IRROFF cannot be activated in

conjunction with REGOFF. This mode is available only on the WLCSP package. It

allows to supply externally a 1.2V voltage source through VCAP_1 and VCAP_2 pins, in

addition to VDD.

VDD minimum value is 1.65V.

The following conditions must be respected in Regulator bypass mode (see Figure8):

–

–VDD should always be higher than VCAP_1 and VCAP_2 to avoid current injection between power domains. External reset should be used to cover both conditions: until VCAP_1 and VCAP_2 reach 1.08V and until VDD reaches 1.65V

PA0 can be used as a standard GPIO pin.

Doc ID 15818 Rev 521/147

205 STM32F205xx207xx参考手册

DescriptionFigure 6.STM32F205xx, STM32F207xxStartup in regulator bypass/regulator off mode: slow VDD slope

Figure 7.Startup in regulator bypass/regulator off mode: slow VDD slope

22/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

2.2.18 Real-time clock (RTC), backup SRAM and backup registers

The backup domain of the STM32F205xx and STM32F207xx includes:

●

●

●The real-time clock (RTC) 4 Kbytes of backup SRAM20 backup registers

The RTC provides a set of continuously running counters which can be used with suitable

software to provide a clock calendar function, an alarm interrupt and a periodic interrupt. It is

clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC

oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a

typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to

compensate for any natural quartz deviation.

The RTC features calendar registers with seconds, minutes, hours, week day, date, month,

year. Two alarm registers are used to generate an alarm at a specific time and calendar

fields can be independently masked for alarm comparison. To generate a periodic interrupt,

a 16-bit programmable binary auto-reload downcounter with programmable resolution is

available and allows automatic wakeup and periodic alarms from every 120 μs to every 36

hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a

time base of 1 second from a clock at 32.768 kHz.

The backup SRAM size is 4 Kbytes and can be enabled by software. When the backup RAM

is enabled the power consumption in Standby or VBAT mode is slightly higher (see

Section2.2.19: Low-power modes).

The backup registers are 32-bit registers used to store 80 bytes of user application data

when VDD power is not present. Backup registers are not reset by a system, a power reset,

or when the device wakes up from the Standby mode (see Section2.2.19: Low-power

modes).

The RTC, backup RAM and backup registers are supplied through a switch that takes power

from either the VDD supply when present or the VBAT pin.

2.2.19 Low-power modes

The STM32F205xx and STM32F207xx support three low-power modes to achieve the best

compromise between low power consumption, short startup time and available wakeup

sources:

●Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can

wake up the CPU when an interrupt/event occurs.

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

●Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of

SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC

Doc ID 15818 Rev 523/147

205 STM32F205xx207xx参考手册

DescriptionSTM32F205xx, STM32F207xxand the HSE crystal oscillators are disabled. The voltage regulator can also be put

either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line. The EXTI line

source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup /

tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup.

●Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal

voltage regulator is switched off so that the entire 1.2 V domain is powered off. The

PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering

Standby mode, the SRAM and register contents are lost except for registers in the

backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset,

a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event

occurs.

Note:1The RTC, the IWDG, and the corresponding clock sources are not stopped when the device

enters the Stop or Standby mode.

2.2.20 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery or an

external supercapacitor.

VBAT operation is activated when VDD is not present.

Note:When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events

do not exit it from VBAT operation.

2.2.21 Timers and watchdogs

The STM32F205xx and STM32F207xx devices include two advanced-control timers, eight

general-purpose timers, two basic timers and two watchdog timers.

Table3 compares the features of the advanced-control, general-purpose and basic timers.

Table 3.Timer feature comparison

DMA Capture/Max Max request compare interface timer outputgenerationchannelsclockclock

Yes4Yes60 MHz120

MHz

60

MHz

60

MHz

60

MHz Counter Counter Prescaler Timer typeTimerresolutiontypefactorAdvanced-TIM1, controlTIM8TIM2, TIM5TIM3, TIM4TIM6, TIM7Up, Any integer Down, between 1 Up/downand 65536Up, Any integer Down, between 1 Up/downand 65536Up, Any integer Down, between 1 Up/downand 65536UpAny integer between 1

and 6553616-bit32-bitYes4No30 MHzGeneral purpose16-bitYes4No30 MHzBasic16-bitYes0No30 MHz

24/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxTable 3.Timer feature comparison (continued)Description

Counter Counter Prescaler Timer typeTimerresolutiontypefactor

Any integer

between 1

and 65536

Any integer

between 1

and 65536

Any integer

between 1

and 65536

Any integer

between 1

and 65536DMA Capture/Max Max request compare interface timer outputgenerationchannelsclockclockNo2No60 MHz120 MHz120 MHz60 MHz60 MHzTIM916-bitUpGeneral purposeTIM10, TIM1116-bitUpNo1No60 MHzTIM1216-bitUpNo2No30 MHzTIM13, TIM1416-bitUpNo1No30 MHz

Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

●

●

●

●Input captureOutput comparePWM generation (edge- or center-aligned modes)One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The TIM1 and TIM8 counters can be frozen in debug mode. Many of the advanced-control timer features are shared with those of the standard TIMx timers which have the same architecture. The advanced-control timer can therefore work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F20x devices (see Table3 for differences).

●TIM2, TIM3, TIM4, TIM5

The STM32F20x include 4 full-featured general-purpose timers. TIM2 and TIM5 are 32-bit timers, and TIM3 and TIM4 are 16-bit timers. The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 32-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.Doc ID 15818 Rev 525/147

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

205 STM32F205xx207xx参考手册

DescriptionSTM32F205xx, STM32F207xxThe TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the

other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the

Timer Link feature for synchronization or event chaining.

The counters of TIM2, TIM3, TIM4, TIM5 can be frozen in debug mode. Any of these

general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are

capable of handling quadrature (incremental) encoder signals and the digital outputs

from 1 to 4 hall-effect sensors.

●TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM10 and TIM11 feature one independent channel, whereas TIM9 has two

independent channels for input capture/output compare, PWM or one-pulse mode

output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured

general-purpose timers. They can also be used as simple time bases.

●TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM13 and TIM14 feature one independent channel, whereas TIM12 has two

independent channels for input capture/output compare, PWM or one-pulse mode

output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured

general-purpose timers.

They can also be used as simple time bases.

2.2.22 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be

used as a generic 16-bit time base.

2.2.23 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is

clocked from an independent 32 kHz internal RC and as it operates independently from the

main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog

to reset the device when a problem occurs, or as a free-running timer for application timeout

management. It is hardware- or software-configurable through the option bytes.

The counter can be frozen in debug mode.

2.2.24 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It

can be used as a watchdog to reset the device when a problem occurs. It is clocked from the

main clock. It has an early warning interrupt capability and the counter can be frozen in

debug mode.

26/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

2.2.25 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard

downcounter. It features:

●●●●

A 24-bit downcounterAutoreload capability

Maskable system interrupt generation when the counter reaches 0Programmable clock source

2.2.26 I2C bus

Up to three I2C bus interfaces can operate in multimaster and slave modes. They can

support the Standard- and Fast-modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

2.2.27 Universal synchronous/asynchronous receiver transmitters

(UARTs/USARTs)

The STM32F205xx and STM32F207xx embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and two universal asynchronous receiver transmitters (UART4 and UART5).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to

communicate at speeds of up to 7.5 Mbit/s. The other available interfaces communicate at up to 3.75 Mbit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

Table 4.

USART feature comparison

Max. baud rate Max. baud rate

Smartcard in Mbit/s in Mbit/s APB (ISO7816)(oversampling (oversampling mapping

by 16)by 8)

X

3.75

7.5

APB2

(max. 60MHz)APB1 (max. 30MHz)APB1 (max. 30MHz)

USART Modem SPI

LINirDA

namefeatures(RTS/CTS)master

USART1XXXXX

USART2XXXXXX1.873.75

USART3XXXXXX1.873.75

Doc ID 15818 Rev 527/147

205 STM32F205xx207xx参考手册

DescriptionTable 4.USART feature comparison (continued)STM32F205xx, STM32F207xxUSART Modem SPI LINirDAnamefeatures(RTS/CTS)masterMax. baud rate Max. baud rate Smartcard in Mbit/s in Mbit/s APB (ISO7816)(oversampling (oversampling mapping

扩展:stm32f207参考手册 / stm32f205参考手册 / stm32f207编程参考

by 16)by 8)

-1.873.75APB1 (max.

30MHz)

APB1

(max.

30MHz)

APB2

(max.

60MHz)UART4X-X-XUART5X-XD-X-3.753.75USART6XXXXXX3.757.5

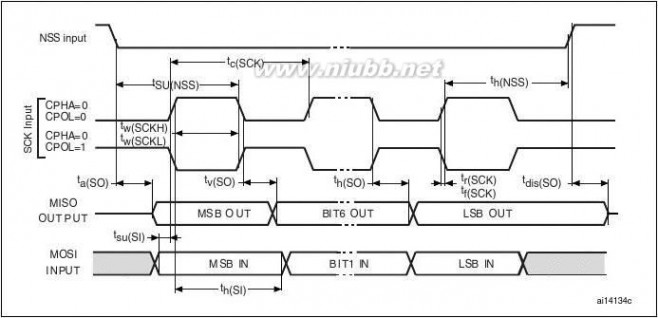

2.2.28 Serial peripheral interface (SPI)

The STM32F20x feature up to three SPIs in slave and master modes in full-duplex and

simplex communication modes. SPI1 can communicate at up to 30 Mbits/s, SPI2 and SPI3 can communicate at up to 15 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master

mode and slave mode.

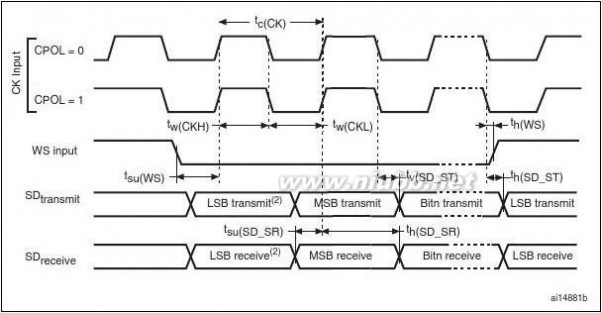

2.2.29 Inter-integrated sound (I2S)

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) are available. They can be

operated in master or slave mode, and can be configured to operate with a 16-/32-bit

resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 96 kHz are supported. When either or both of the I2S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling

frequency.

2.2.30 SDIO

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System

Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus

modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.28/147Doc ID 15818 Rev 5

205 STM32F205xx207xx参考手册

STM32F205xx, STM32F207xxDescription

2.2.31 Ethernet MAC interface with dedicated DMA and IEEE1588 support

Peripheral available only on the STM32F207xx devices.

The STM32F207xx devices provide an IEEE-802.3-2002-compliant media access controller

(MAC) for ethernet LAN communications through an industry-standard medium-

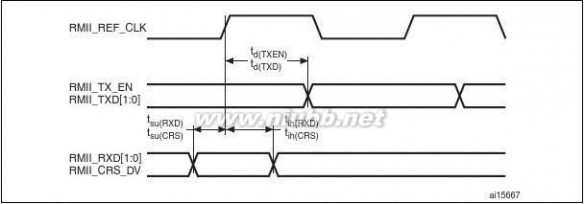

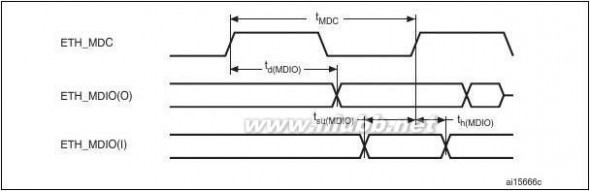

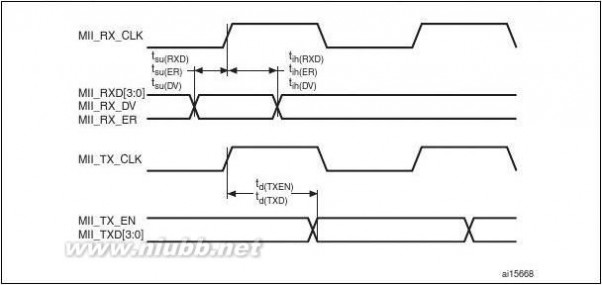

independent interface (MII) or a reduced medium-independent interface (RMII). The

STM32F207xx requires an external physical interface device (PHY) to connect to the

physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F207xx MII

port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz

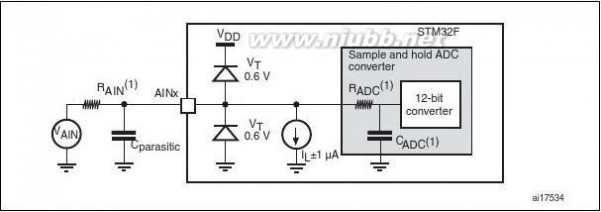

(MII) or 50 MHz (RMII) output from the STM32F207xx.

The STM32F207xx includes the following features:

●

●Supports 10 and 100 Mbit/s ratesDedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F20x and STM32F21x reference manual for

details)

Tagged MAC frame support (VLAN support)

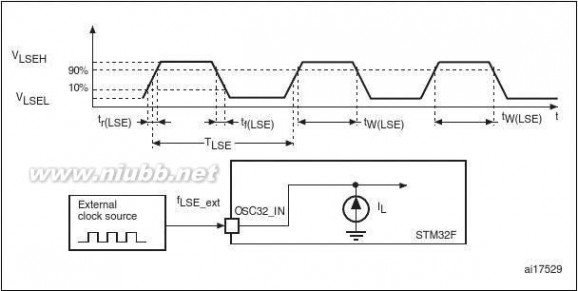

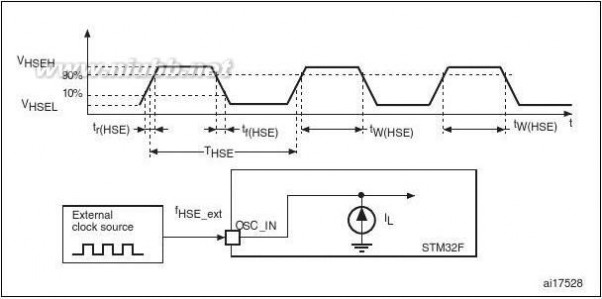

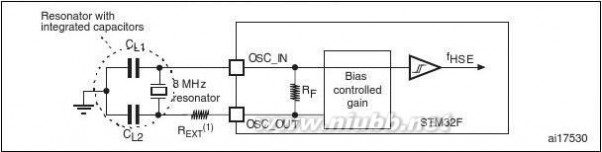

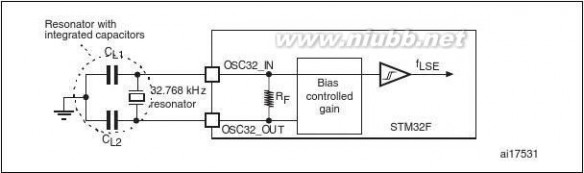

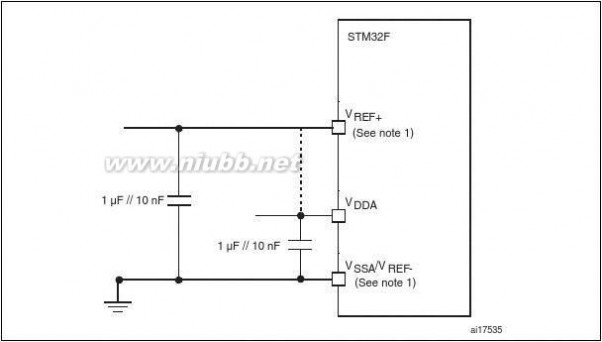

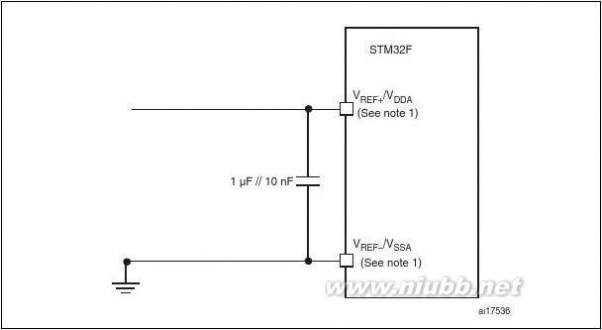

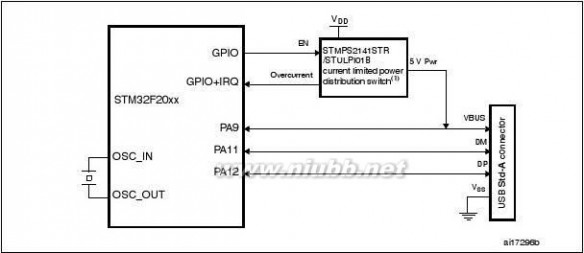

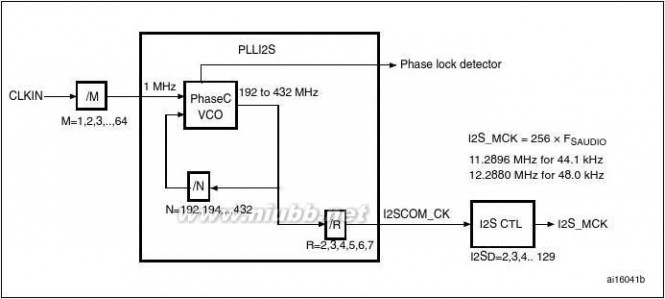

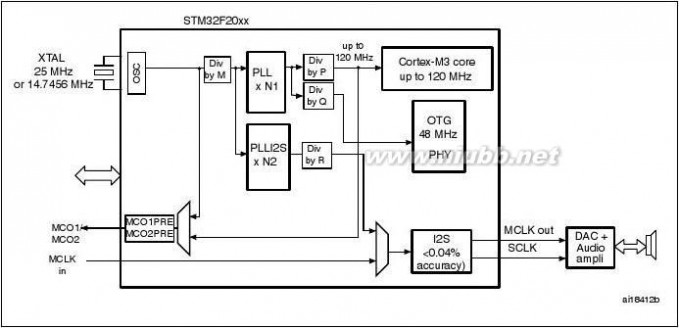

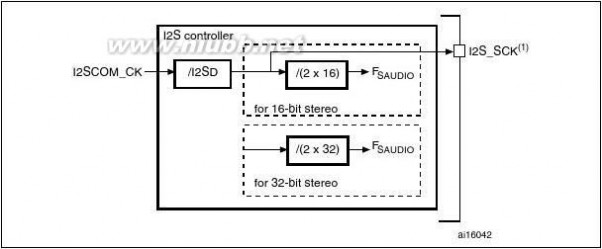

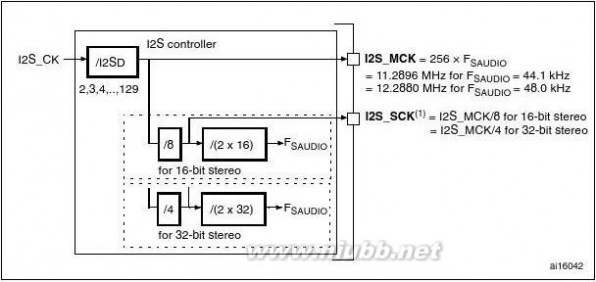

Half-duplex (CSMA/CD) and full-duplex operation